基于CPLD的片内环形振荡器的设计方案

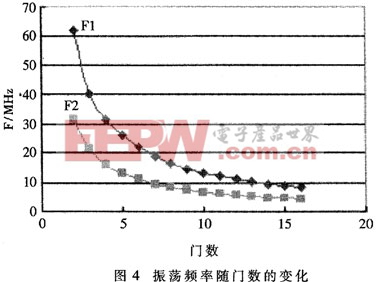

表1数据表明,通过增加门电路的数量可以有规律地减小振荡电路的工作频率,由每个逻辑单元实现的门电路单元延时tpd在7.5~10ns之间。

本文介绍的基于CPLD的片内振荡器设计方法,在改变该振荡器电路中门电路数量时,可以有规律地将振荡频率控制在8MHz~62MHz范围内。振荡器的片内设计使基于CPLD的片上系统(SoC)设计无需外接时钟信号源,加大了系统的集成度并降低了设计成本。本方法有很大的通用性,可以方便地在不同CPLD芯片间移植。仿真和测试数据表明该设计方法具有正确性和可行性。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码