基于Xtensa可配置处理器技术的视频加速引擎技术开发

4、自动化软件开发工具套件支持

可配置和可扩展的关键是不仅能够自动产生预先经过验证的RTL代码,用于设计人员定制处理器(包括所有系统扩展功能),而且还能够自动产生完整的软件工具,包括一个与处理器相匹配并经过优化的开发工具套件、一个基于时钟周期的指令集仿真器以及系统模型。

这种自动化意味着编译器知道设计人员所添加的新指令、相关的寄存器以及寄存器文件。因此,编译器能够对用户定义的指令进行调度,并执行寄存器分配操作。类似地,软件开发人员在调试时除了处理器本身的基本寄存器,还能够了解设计人员定义的寄存器和寄存器文件;同时,软件开发人员能够利用指令集仿真器对设计人员定义的新指令进行仿真。与处理器相关的实时操作系统RTOS端口和系统模型也能够自动产生。Tensilica的软件工具能够在一个小时内自动产生上述软件工具,这是对使用可配置处理器用户的核心承诺,能够执行诸如SAD运算,而不必采用RTL那样的实现方法。

5、采用可配置处理器构建视频加速引擎建立多操作功能部件

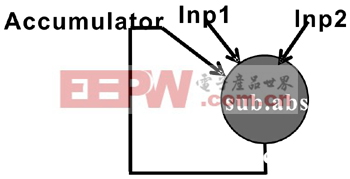

将SAD这样的融合操作加到一个可配置处理器中是一件麻烦的事情。一条称为“sub.abs.ac”的新指令可以完成“减法-绝对值-累加”运算操作。这条新指令能够将图2中的操作变成图3中的复操作。

图3 使用新指令计算“减法-绝对值-累加”操作

将该指令添加到处理器中后,C编译器能够识别这条新的“sub.abs.ac”指令,并调度相关指令;调度器将显示“sub.abs.ac”功能部件所使用的内部信号;汇编器能够处理这条新指令;指令集仿真器ISS能够按照时钟周期模式进行仿真。

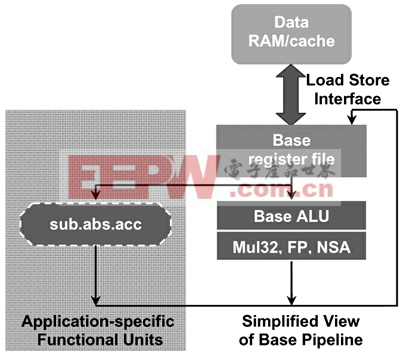

新的专用视频功能部件插入处理器后的数据通路简图如图4所示。注意到,除了产生功能部件逻辑外,硬件生成工具还能够自动插入前馈通路、控制逻辑以及旁路逻辑,以便将新的功能部件与数据通路中的其它逻辑互连。

图4 插入sub.abs.ac视频专用功能部件后的简化数据通路示意图

包含新指令的C代码描述的SAD算法如下:

for (row = 0; row numrows; row++) {for (col = 0; col numcols; col++) {

sub.abs.ac( accum, macroblk1[row][col], macroblk2[row][col]);

} /* column loop */

} /* row loop */

正如前面提到的,对于一个16x16宏块而言,增加新指令后程序主循环中的操作数减少到256个(即numrows = numcols = 16)。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码