带宽自适应全数字锁相环的设计与实现

3 带宽自适应全数字锁相环的软件仿真和FPGA实现

3.1 带宽自适应全数字锁相环的软件仿真

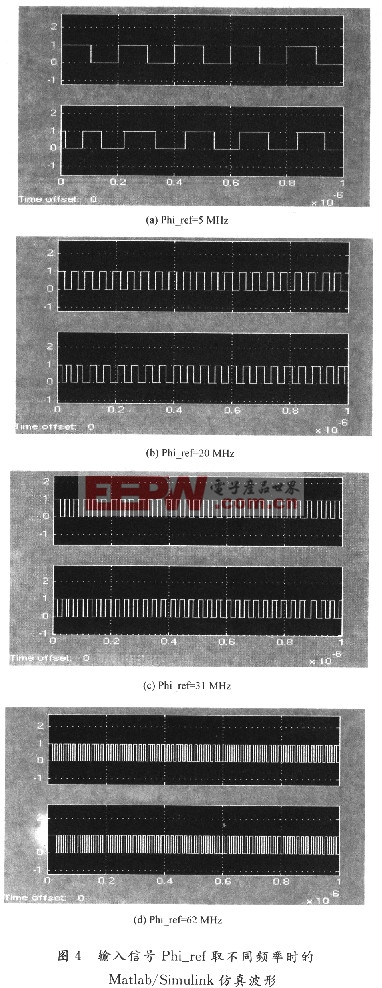

在图3建立的模型基础上,该设计首先对带宽自适应全数字锁相环进行了软件仿真,主要包括Matlab/Simulink仿真和QuartusⅡ时序仿真。其中系统的各个参数为:阻尼系数ζ=O.707,系统时钟周期Tclk=1/fs,采样频率fs=250 MHz。图4为输入信号Phi_ref取不同频率时的Matlab/Simulink仿真波形。

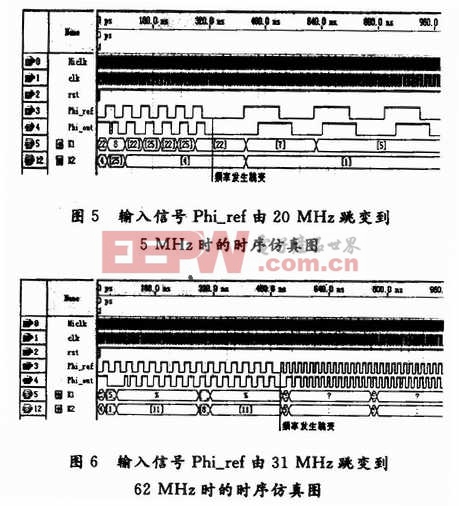

使用DSP Builder库中的Signal Compiler模块将图3建立的全数字锁相环模型转化为VHDL语言代码。该设计通过QuartusⅡ软件完成带宽自适应全数字锁相环的整体时序仿真。图5为输入信号Phi_ref由20 MHz跳变到5 MHz时的时序仿真图;图6为输入信号Phi_ref由31 MHz跳变到62 MHz时的时序仿真图。通过对所设计的全数字锁相环的Matlab/Simu-link仿真和QuartusⅡ时序仿真可以看出:该系统能够实现锁频的功能;同时该系统具有自适应的特性,在输入信号很大变化范围内都具有良好的性能;最后该系统对频率发生阶跃跳变的输入信号亦具有很好的跟踪性能。

3.2 FPGA实现及硬件测试

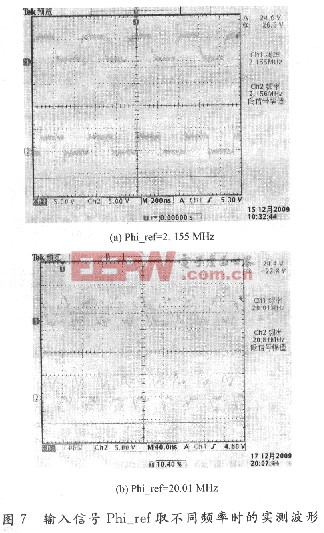

由于Signal Compiler模块可以自动地将DSPbuilder建立的模型文件转化为QuartusⅡ环境下的工程文件,因此,该设计在完成软件仿真后结合FPGA试验箱,在生成的工程下进行引脚的锁定、编译适配下载到FPGA芯片,实现所设计的带宽自适应全数字锁相环,并完成硬件测试。在硬件测试中需要用到信号发生器和示波器,信号发生器用来产生锁相环的输入测试信号,示波器用来观测锁相环的输入/输出波形。图7为输入信号Phi_ref取不同频率时的实测波形。

以上的软件仿真与硬件测试都表明,设计的带宽自适应全数字锁相环系统能过实现锁频的功能,设计是成功可行的。

4 结语

本文使用DSP Builder建立系统模型完成全数字锁相环设计,理论分析和仿真结果基本一致。从以上设计过程可以看出:基于DSP Buil-der完成全数字锁相环设计的方法,使得设计者可以利用Simulink快捷灵活的建模仿真功能和Matlab强大的数据分析能力进行FPGA系统级的建模仿真,并使得设计者从编写VHDL或者Verilog HDL等代码语言的繁琐工作中解放出来,而专注于在Matlab/Simulink下搭建系统模型的工作上,缩短了设计周期,提高了设计的灵活性。

关键词: DSP-Builder 带宽自适应 PI控制 全数字锁相环

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码