基于FPGA的恒温晶振频率校准系统的设计

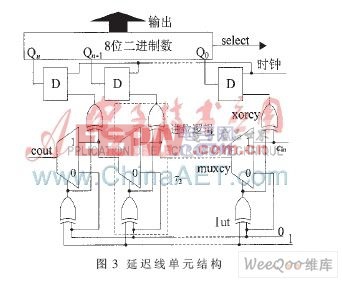

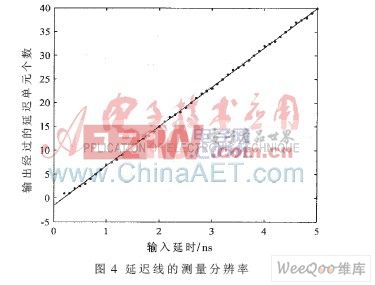

在XILINX公司FPGA的单元结构中,为了实现快速的数学运算设置了许多专用的进位逻辑资源。这些进位逻辑的延时很小,而且它们之间可以相互连接组成进位线,可以使用这种专用的进位线作为延迟线来实现时间内插。如图3所示,设计中使用了Spartan-3系列的FPGA中专用的进位逻辑逐个连接组成延迟线,一个进位逻辑由查找表(LUT)、专用选通器(MUXCY)和专用异或门(XORCY)三部分构成。其总体结构上类似一个多位二进制加法器,两个输入的各位分别被置为1和0,进位信号没来时加法器各位均为1。当进位信号到来时就会沿着进位线一级一级地传输,加法器每一位输出值的变化就代表着信号的延迟信息,时钟前沿到达时就可以将这些信息锁存入触发器中。图4是在一个时钟周期的仿真中延迟线单元输出经过的延迟单元的个数,进行直线拟合后的结果为:

所以延迟线单元的测量分辨率约为1/8.257 4=0.121 ns.

1.4 计数器模块的设计

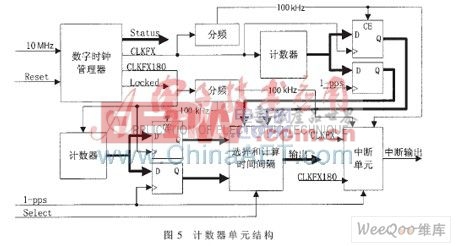

图5简单描述了计数器模块的基本构造。在计数器模块的设计中,使用了Spartan-3系列的数字时钟管理器,主要目的是将晶振时钟信号倍频后作为计数器的工作时钟,保证时钟周期小于延迟线的总延时。根据时序仿真所确定的延迟线单元的测量分辨率及长度参数,将晶振频率倍频为200 MHz。

时钟前沿附近计数器输出为亚稳态,如果1-pps信号恰好在这个时刻到达,便会将错误的计数值锁存。为了解决这个问题,模块中使用数字时钟管理器输出相位差为180°的两路时钟,分别驱动两个计数器同时工作,这样无论任何时刻都能保证其中之一的输出为正确值,之后再对两者进行判断选择。选择信号由延迟线单元提供,通过统计1-pps信号经过延迟单元的个数来确定1-pps信号与时钟前沿的时差,然后输出select信号。

两个计数器进行循环计数,每个计数器都连接着两组寄存器,其中一组将GPS秒脉冲信号作为工作时钟;另一组的时钟信号与对应计数器的时钟相连接,且其使能端与100 kHz分频信号相连。当GPS秒脉冲和100 kHz信号到来时,便会将计数值送入相应的寄存器组。这样可以充分利用FPGA的全局时钟资源,使相应的寄存器组都使用同一时钟,保证寄存器触发的同步性。此外,使用循环计数的方式也解决了传统起停型计数器由于启动和停止信号不满足建立保持时间而造成计数器输出错误的问题。当1-pps信号与100 kHz信号的前沿都到达后,中断单元将输出中断信号,用于通知PicoBlaze软核读取测量结果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码