多锁相环和扩频时钟在数字娱乐设备中的必威娱乐平台

随着集成技术的不断发展,基于锁相环(PLL)的硅芯片时序解决方案的应用越来越普遍,为那些需要多种频率的设计方案提供了更洁净、更稳定的时钟选择方案。本文的目的在于详细论述采用硅芯片时序解决方案来解决时序设计难题时所持的价值主张,并与采用多个独立晶体或晶体振荡器(XO)的传统设计方法进行了对比。

1. 高清电视系统中采用多种频率的需要——不同的标准和接口

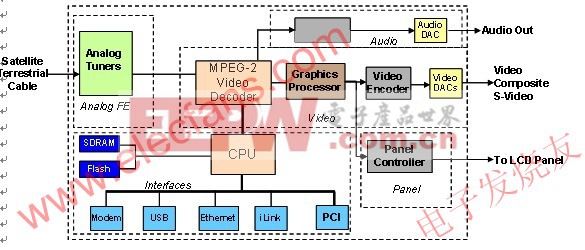

图1所示为液晶电视机天线的基本原理图,简单地说明了数字电视将输入的数字数据流处理成适于用户起居室内电视机使用的正确音频和视频格式的流程。

图1:常见液晶电视机体系架构

调谐电路板上加入了多个子系统。各项基本功能从广义上可以归类到以下几种模块下:

1.模拟前端(解调器)

2.音频/视频编码和解码(MPEG视频解码器/MPEG音频解码器)

3.各类接口

4.显示屏

上图中所显的所有模块几乎都需要时钟信号。CPU要求的时钟信号典型范围为30 – 100MHz。MPEG标准要求采用基于27MHz的时钟输入。其中存在需要解码器和编码器同步的必要功能,而这项功能由VCXO(电压控制晶体振荡器)来实现。对于作为数模转换器(DAC)时钟源的音频时钟,其ppm要求极为严格。这些频率取决于采样频率和过采样比率。对于各类接口来说,时钟信号由各自的标准来决定,诸如USB、以太网、调制解调器、PCI、PCIExpress、SATA等等。

显示屏的时钟取决于屏幕尺寸以及显示标准(高清(HD):1080i、1080p、720p;标清(SD):NTSC、PAL)。屏幕控制器子系统的基本系统是将输入图像数据转换成实际屏幕尺寸,例如,采用74.17582418 MHz等时钟。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码