基于DSP Builder的带宽自适应全数字锁相环的设计与实现

分析式(5)中得到的两个参数K1和K2,若式中c和ζ为常数,则参数K1和K2的变化只与输入信号频率ωref的变化有关,因此,得到的全数字锁相环模型具有自适应的特性,这是传统的全数字锁相环不具有的新特点。

2 带宽自适应全数字锁相环的DSP Builder建模

2.1 DSP Builder介绍

由于FPGA广泛应用,使得EDA软件QuartusⅡ在很多领域中显得尤为重要,目前全数字锁相环的设计多是通过EDA技术完成,使用FPGA予以实现。这就需要设计者对FPGA硬件电路及硬件描述语言VHDL或者Verilog HDL非常熟悉;同时,由于在QuartusⅡ环境下使用硬件描述语言进行编程设计系统模块时相当繁琐。而Matlab在搭建系统的数学模型方面功能强大,具有专门的建模仿真工具Simulink,可以进行图形化的建模仿真。但是Matlab本身不支持硬件电路,只能完成单纯的数学模型的建模、仿真。如果把两者的优势结合起来,使二者扬长避短,则可以使复杂的电子系统的设计变得相当容易且直观。

DSP Builder是Altera公司推出的一个面向DSP开发的系统工具。它是作为Matlab的一个Simulink工具箱出现的,可以在atlab/Simulink环境下进行图形化建模仿真。DSP Builder中的模块是以算法级的描述给出的,易于用户从系统或者算法级进行建模,甚至不需要十分了解FPGA本身和硬件描述语言。在DSPBuilder的模块库中还提供Matlab和QuartusⅡ的接口模块Signal Compiler,利用该模块可以方便地把在Ma-tlab/Simulink环境下建立的算法或者系统级模型转化为FPGA可编译的后缀为.vhd的VHDL语言程序。在QuartusⅡ中打开工程文件,可以对生成的程序进行编译、时序仿真,完成后可以结合FPGA开发板的引脚情况锁定引脚,经过编译、适配后即可下载到FPGA开发板上完成硬件测试和硬件实现。

2.2 带宽自适应全数字锁相环的DSP Builder建模

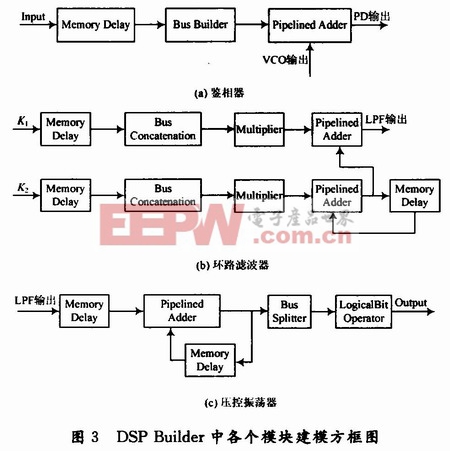

该设计方法就是在Matlab/Simulink环境下借助DSP Builder简单、方便快速地建立上述分析得到的全数字锁相环的数学模型,各个模块建模方框图如图3所示。按照以上各个模块方框图连接,构成整个系统模型,并加入系统时钟Clock模块和Signal Compiler模块,即完成整个系统的。DSP Builder建模。其中输入信号K1和K2是由式(5)计算得到,用6位无符号整数表示,K1和K2可以随着输入信号Phi_ref频率的变化而自适应的做出调整;Phi_ref和Phi_out分别为环路的输入和输出信号,都采用1位无符号的整数表示。

3 带宽自适应全数字锁相环的软件仿真和FPGA实现

3.1 带宽自适应全数字锁相环的软件仿真

在图3建立的模型基础上,该设计首先对带宽自适应全数字锁相环进行了软件仿真,主要包括Matlab/Simulink仿真和QuartusⅡ时序仿真。其中系统的各个参数为:阻尼系数ζ=O.707,系统时钟周期Tclk=1/fs,采样频率fs=250 MHz。图4为输入信号Phi_ref取不同频率时的Matlab/Simulink仿真波形。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码