等精度频率计的实现

等精度测频的原理图如图2所示。图中,预置软件闸门信号GATE是由FPGA的定时模块产生,GATE的时间宽度对测频精度的影响较少,故可以在较大的范围内选择。这里选择预置闸门信号的长度为1s。图中的CNT1和CNT2是2个可控的32位高速计数器,CNT1_ENA和CNT2_ENA分别是其计数使能端,基准频率信号f0从CNT1_CLK输入,待测信号fx从CNT2的时钟输入端CONT2_CLK输入,并将fx接到D触发器的clk端。测量时,由FPGA的定时模块产生预置的GATE信号,在GATE为高电平,并且fx的上升沿时,启动2个计数器,分别对被测信号和基准信号计数,关闭计数闸门必须满足,GATE为低电平,且在fx的上升沿。若在一次实际闸门时间Tx中,计数器对被测信号的计数值为Nx,对标准信号的计数值为N0,而标准信号的频率为f0,则被测信号的频率为fx,则fx=(N0/Ns)f0。图2中的所有功能都在FPGA端实现。

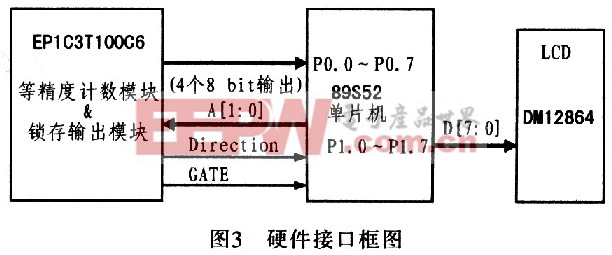

图2所示的单元完成了等精度测频的核心部分,在实际应用中多数时候需要将测量的结果通过显示设备进行显示。从图2可以看出本设计由于设计了锁存单元,将计数结果和一些控制信号进行了锁存处理,便于与单片机或者其他的单片机(MCU)相连,因此在该FPGA实现的核心单元基础上连接MCU,容易实现计数值到实际频率值以及相应的周期值之间的转换,并通过MCU控制显示设备将最终需要显示的结果信息进行显示。FPGA器件与单片机硬件接口电路框图如图3所示。图3中的等精度频率测量模块和锁存模块都由Altera公司的FPGA器件EP1C3T100C6实现,等精度计数模块的输出结果为2个32 bit的数据,为了方便与单片机连接,该2个32 bit数据由在FPGA器件内部的锁存器分8次锁存输出,单片机每次读取8 bit,连续读取8次即可,读取的Nx和N0的计数值经过单片机按照等精度频率计算公式换算成实际频率值,最后通过DM12864进行显示。

3 测量结果的误差分析

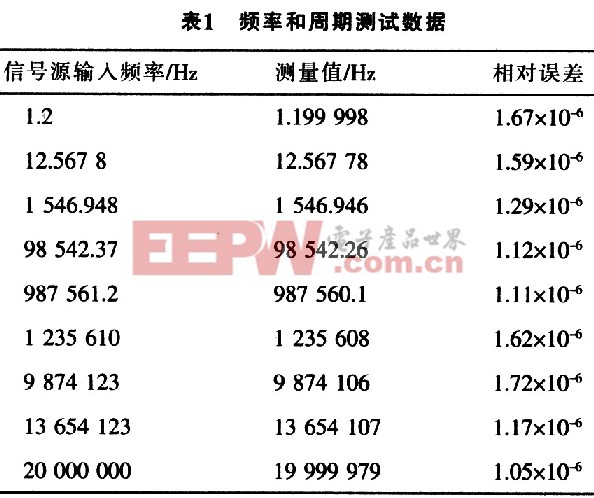

采用高精度信号源输出不同频率的正弦波信号,经过信号调理电路,整形得到的方波信号提供给FPGA进行计数测量,将测量结果与高精度信号源输出的频率相比较,计算其误差,如表1所示。

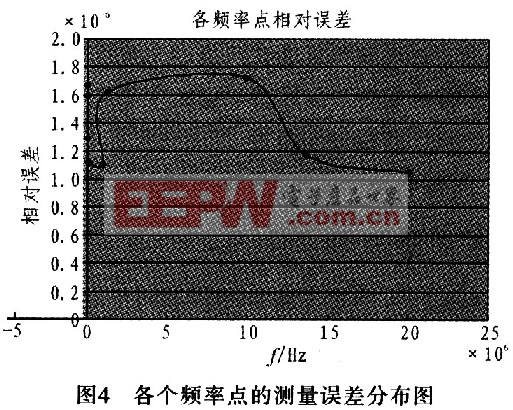

表l给出了各种频率的测量结果和误差。结果显示,本设计在1Hz~20MHz全范围内的测量误差小于2×10-6。从图4可以看出测量结果的误差分布在同一个数量级附近,达到了等精度测量的目的。在实际测试中发现,如果提高系统晶振的频率或者提高晶振的精度级别,频率测量的误差还会进一步降低。

4 结束语

详细介绍了等精度测量的原理,并给出等精度测量的思想在FPGA上实现的方法。测试结果表明该等精度测量方案误差非常小,在测量范围内误差恒定。该设计方案对测量频率实现设计具有一定的借鉴。

关键词: 等精度频率计

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码