随机脉冲信号采集卡的设计

3 系统硬件电路设计

该系统硬件电路主要包括单片机主系统中的随机脉冲放大及限幅电路、脉冲幅度、脉冲宽度测量电路、高速信号采集及存储电路及由EPLD等构成的控制信号电路等。

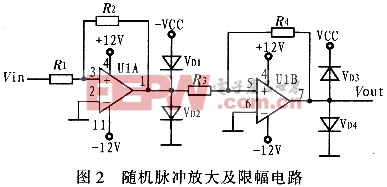

3.1 随机脉冲放大及限幅电路

随机脉冲放大及限幅电路完成脉冲信号的放大、限幅及整形,以满足TTL输入端信号的要求。图2为随机脉冲放大及限幅电路,采用高速运算放大器OPA603,其特点是频带宽且转换速率较高,适用于脉冲放大类电路。输入的脉冲信号通过两级放大及限幅后。输出的脉冲信号送到80C196的高速输入器件的输入端。

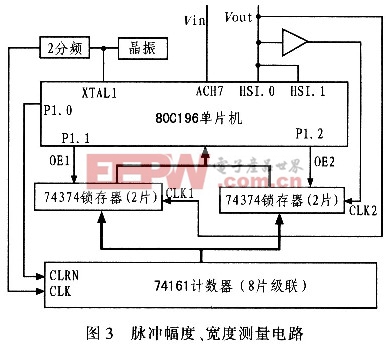

图3为脉冲幅度及宽度测量电路示意图。单片机(80C196)内置的10位A/D转换电路完成脉冲幅度的测量。由74LSl61构成的脉冲计数电路测量脉宽。主系统电路负责整个系统的控制、采样频率的设置及相关的数据处理及控制传送等。其工作原理为:随机脉冲信号(Vin)送入80C196的模拟信号输入端ACH6,然后由80C196的内部的10位A/D转换器进行采样和转换同时该随机脉冲信号经放大、限幅并整形后的脉冲信号(Vout)送高速输入器件的HSI0、HSIl端,作为脉冲前后沿的触发事件,启动中断处理程序。HSI0输入端作为脉冲信号的前沿(上升沿)事件触发输入端,用于读出并记录脉冲前沿到达的时刻及启动A/D转换器进行采样和转换;HSIl输入端作为脉冲信号的后沿(下降沿)事件触发输入端,用于读出并记录脉冲后沿到达的时刻及读取A/D转换器的值。另外整形后的脉冲信号(Vout)有一路信号(CLKl)送到一组7415374(4片)的CLK端,用于锁存74Lsl61计数器的计数值(即脉冲前沿到达的时刻)。通过反相器输出的另一路信号(CLK2)送到另74LS374(4片)的CLK端,用于锁存74LSl61计数器的计数值(即脉冲后沿到达的时刻)。脉冲信号的宽度即为2个计数值的差值。

3.2 高速信号采集及存储电路

高速信号采集及存储电路用于采集卡在采集方式下时采集输入脉冲的脉内波形数据。采用8位高速A/D转换器TLC5540,其最大转换速度40 MS/s,模拟输入带宽大于75 MHz,具有内部采样和保持功能。

TLC5540进行转换所需时钟信号频率可由单片机设置。A/D转换后的数据自动存储在外接的62256存储器中,其地址信号由4个74LSl61产生。其工作原理为:首先QCLR输出一个负脉冲,将74LSl61计数器清零,然后再设置采样时钟信号(TCLK),启动TLC5540进行转换,同时将RAD信号设为有效(低电平),产生的数据在脉冲信号(Vout为高电平)出现时按顺序写入外接的62256存储器中,脉冲信号(Vout为低电平)消失则自动停止写入。高速RAM的地址信号由74LSl61地址产生器提供。对每个脉冲信号期间采样的次数可根据2个脉冲信号最后写入地址的差值进行来计算,即由单片机读出的该脉冲信号下降沿时刻74LSl61的计数值(即最后写入的RAM的地址),再减去上一次读出的值,即为该脉冲的采样次数。连续采样一群脉冲的波形数据后需暂停采集,将采集的每个脉冲的波形数据与该脉冲的其他参数(如脉冲宽度、脉冲到达时间等)按规定的格式组合后送到与主机交换数据的FIF0高速存储器中,供主机读取和处理,数据送完后再启动采集下一群脉冲。一群脉冲的数量由用户根据实际情况确定,以连续采集的波形数据存入高速RAM中不产生溢出为最大限。图4为高速信号采集及存储电路。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码