高速高精度流水线模数转换器的设计

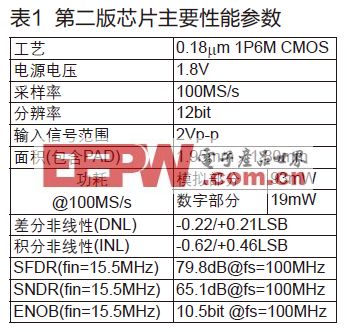

对比版图修正前后两版芯片的测试结果,我们可以发现修正后ADC的INL从原来的-5.0/+4.8LSB降低为-0.62/+0.46LSB,在2.41MHz输入,100MHz采样率下SNDR和SFDR分别从原来的57.9dB和68.9dBc提高到67.5dB和87.2dBc。所以说,本文对寄生电阻的分析是合理的,对应的修正措施也是行之有效的。

结语

本文给出了两次流片的测试结果,着重分析了第一版芯片性能不太理想的原因,指出问题出在版图设计中的寄生电阻效应,并用MATLAB行为级建模验证了这种效应对ADC性能的影响。根据分析结果,第二版芯片版图相应地作了修正并再次流片,测试结果表明本文对寄生电阻的分析是合理的,对应的修正措施也是行之有效的。修正后ADC的INL从原来的-5.0/+4.8 LSB降低为-0.62/+0.46 LSB;在2.41MHz输入,100MHz采样率下SNDR和SFDR分别从原来的57.9dB和68.9dBc提高到67.5dB和87.2dBc。该ADC是在0.18mm CMOS工艺下加工的,总面积为3.51mm2,电源电压为1.8V,功耗仅112mW。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码