高速突发模式误码测试仪的FPGA实现方案

摘要:突发模式误码测试仪与一般连续误码测试仪不同,其接收端在误码比对前要实现在十几位内,对具有相位跳变特点的信号进行时钟提取和数据恢复,并且在误码比对时须滤除前导码和定界符,仅对有效数据进行误码统计。本文提出一种基于FPGA实现的高速突发模式误码测试仪设计方案,并介绍该方案的总体设计过程,以及FPGA中主要功能逻辑模块的工作原理和控制系统的设计。该测试仪应用于1.25 GHz GPON系统突发式光接收模块的误码测试中,具有较好的性能和实际意义。

关键词:突发模式;误码测试仪;时钟相位对齐;高速串行收发器

引言

无源光网络PON以其独特的优势在网络中已经规模化地应用。由于GPON系统在现有PON系统中带宽利用率最高,系统成本最低,且具有全业务支持能力,因此其前景被普遍看好,成为众多电信运营商和设备制造商推崇的宽带接入技术。

在GPON中,下行数据是以广播形式发送的,上行数据由多个用户终端按时分多址的方式发送的数据包组成。因传输路径不同,各数据包有不同衰减,不同数据包相位间存在跳变,数据包中存在长连“1”、“0”,这些因素的影响使得OLT突发接收模块接收的信号是特殊的突发光信号。对于上行的突发信号,OLT突发接收模块不仅要从中恢复出幅值相等的信号,而且要消除相位突变,即完成时钟和相位的对齐,因此OLT输出的信号应该为幅值相等且时钟和相位对齐的电信号。本突发模式误码测试仪的作用是,准确地判断被测的OLT突发接收模块的完成幅值恢复响应时间和其可靠性。

1 突发模式误码测试原理

与一般连续误码测试仪相同的是,突发误码测试仪也由发送和接收两部分组成。发送部分发送可预知的信号作为测试信号来模拟实际信道中传输信号,并将该信号送到待测设备中;接收部分产生与发送部分相同的信号,用以和接收的信号逐位比对,并统计误码数和误码率。

与一般连续误码测试仪不同的是,突发误码测试仪发送部分发送的测试信号要模拟突发信号,即具有相位突变和幅度不均衡的特点。此外,接收部分要从接收到的可能存在相位跳变信号中准确地提取时钟和恢复数据。

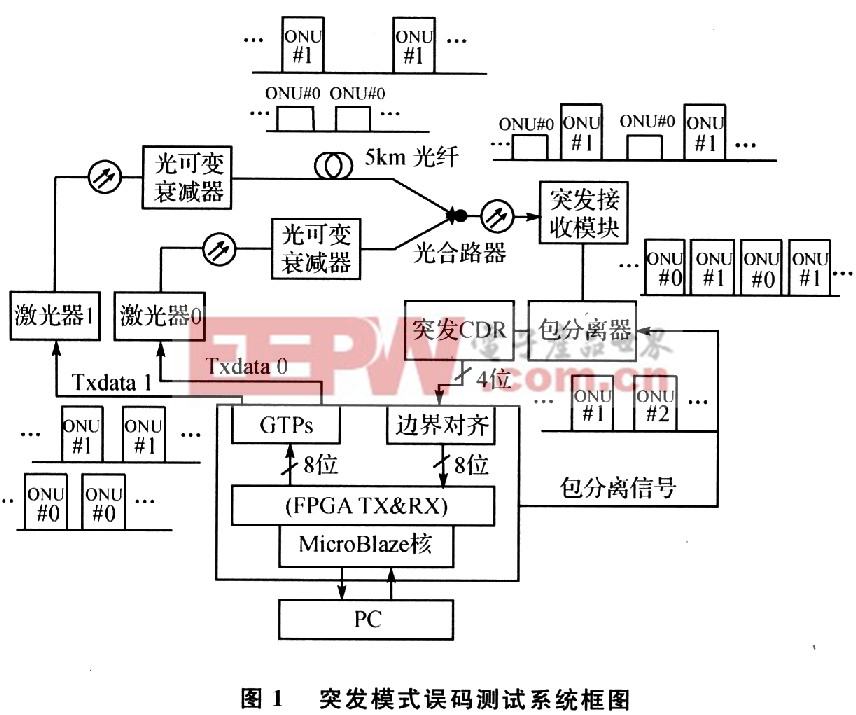

根据突发误码测试仪的特点,其总体设计框图如图1所示。

突发接收模块(BMRx)是要测试的模块。突发误码测试仪用FPGA逻辑来实现两路时分复用(TDMA)数据的输出,两路数据先分别通过光可变衰减器不同幅度的衰减后,再经过不同长度的光纤的时延,最后经过光合路器合为1路信号输出。光合路器的输出数据近乎于实际GPON中的上行突发信号,且假定信号在经过这些路径后没有出现误码。模拟的突发信号在经过待测突发接收模块后,经过包分离电路提取1路包数据(ON-U#1或ONU#2),该路包数据最后经过突发模式时钟数据恢复芯片提取出时钟和4路并行数据。FPGA将提取的时钟作为误码比对的源时钟,并将4路并行数据重构造后与本地产生的数据进行比对,统计误码。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码