降采样FIR滤波器的设计与硬件实现

由图6所示的仿真结果可见,在降采样控制器的控制下,输入滤波器的数据经过滤波器之后,其输出频率降低一半。

3.3 综合、布局和布线结果

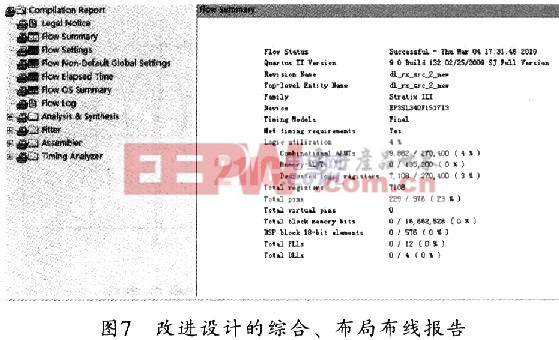

上述设计可用QuartusⅡ9.O进行综合、布局和布线,选用stratixⅢ的器件EP3SL340F151713,所得到的硬件资源占用情况如图7所示。此时,该滤波器最高可以run到170.07 MHz,可以符合系统要求。

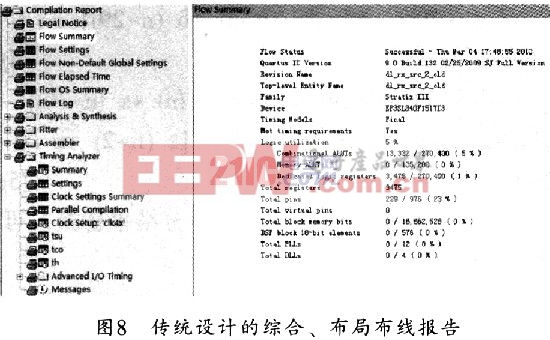

实际上,用OuartusⅡ9.0也可以对传统方法设计出的滤波器进行综合、布局布线,并选择同样的器件。因为,传统的设计只是利用了系数的对称特点,而没有对系数进行分解。由于是直接和输入相乘叠加,因此滤波器的硬件代码最高只能跑到59.51MHz。其硬件资源占用情况如图8所示。

比较图7和图8的报告结果可见,本文提出的设计方法在LUT资源的占有和滤波器最高工作频率方面都有明显的改进。从而解决了传统设计需要专门对滤波器输出信号进行2倍降采样而耗费硬件资源的问题。

4 结束语

本文通过基于matlab自带的工具来对降采样FIR数字滤波器进行原型设计,给出了硬件资源占用少且工作频率高的降采样滤波器的实现方

案。该设计经过modelsim软件的功能仿真和QuartusⅡ软件进行综合、布局布线验证,其均可达到系统要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码