基于FPGA的移位寄存器流水线结构FFT处理器设计与实

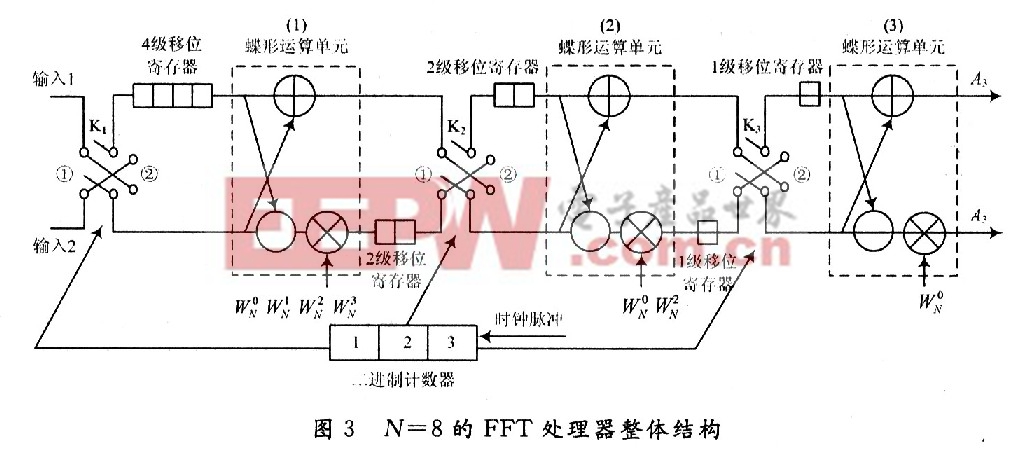

基于上述基本原理,将这种移位寄存器结构扩展到整个FFT系统的各级,可以发现各级使用的移位寄存器数量是递减的。现使用一个8点结构来进行说明。

如图3所示,数据由输入l和输入2进入第一级。通过开关进行选通控制。由于是N=8的运算,所以各级分别加入4级、2级和1级的移位寄存器。

分两路来说明运算过程:

将K1打到位置①,第一路数据进入移位寄存器,待第一路的前4个数据存入4级移位寄存器后,第一路进入的第5个数据与移位寄存器移出的第1个数据进行蝶形运算。

由于输出结果有上下两路,第二级是一个四点的DFT,所以对于上路的输出结果x0(0)+x0(4)类似于第一级,直接存入下一级寄存器,为四点运算做准备,下路的输出,![]() 先存入本级2级移位寄存器中,等到上路的四点运算开始,第二级的移位寄存器有空白位时,移入第二级,为下路的四点运算做准备。所以第一级蝶形运算上路输出前N/4=2个进入下一级寄存器,下路输出的数据依次存入本级移位寄存器中。

先存入本级2级移位寄存器中,等到上路的四点运算开始,第二级的移位寄存器有空白位时,移入第二级,为下路的四点运算做准备。所以第一级蝶形运算上路输出前N/4=2个进入下一级寄存器,下路输出的数据依次存入本级移位寄存器中。

当第一级的输出前N/4=2个数据x0(0)+x0(4)和x0(1)+x0(5)存入第二级移位寄存器时,运算便可以开始,这时开关K2打到位置②,此时第一级上路输出的数据x0(2)+x0(6),即第一级上路输出的第三个数据与第二级移位寄存器移出的第一个数据,即x0(O)+x0(4)进行蝶形运算,输出的第四个数据x0(3)+x0(7)与x0(1)+x0(5)进行蝶算。在这个运算过程中,第一级的2级移位寄存器移出数据依次移位存入到第二级的移位寄存器产生的空白位中。

两个时钟后,第一级上路输出的四个数据完成了蝶形运算,K2打到位置①,在接下来的两个时钟里,第一级中2级移位寄存器的输出依次与此时第二级中2级移位寄存器的输出数据进行蝶形运算,即![]() 与

与![]() ,

,![]() 与

与![]() 完成第一级下路输出的四个数据的蝶形运算。

完成第一级下路输出的四个数据的蝶形运算。

此时,第一路在第一级运算后的输出数据,在第二级完成了全部的蝶形运算。第二级的输出结果同第一级一样,蝶形运算的上路输出前N/8=1个进入下一级寄存器,后一个数据直接进入后一级进行碟算,下路输出的数据存入本级移位寄存器中。

第三级的运算与第二级和第一级类似,即移入1级寄存器的数据与其后一个数据进行碟算,同时使前一级寄存器的输出数据进入后一级寄存器的空白位中,然后开关打到位置②,对下路输出数据进行碟算。

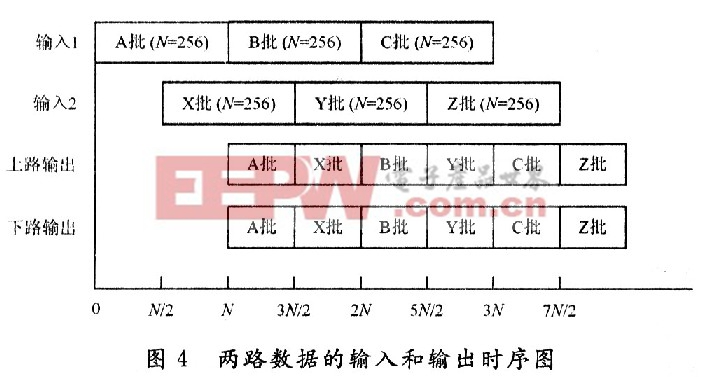

对于第二路数据,通过开关控制,在第二级中,待第一路第一级下路输出数据进行蝶形运算时,移入寄存器的空白位,为运算做准备,由于前级运算周期是后级运周期的两倍,对于第二级碟算模块而言,数据仍然是不间断输入的。通过这样两路数据的交替运算和存储,实现“乒乓操作”,从而提高了蝶形运算模块的运算效率。图4是256点FFT的具体运算输入和输出时序图。对于只有一路数据的应用场合,可以在前级加入,门控开关和数据缓冲寄存器分成两路数据,实现一路数据的不间断读入。

由于采用移位寄存器结梅,各级寄存器使用的数量都是固定的,即为N/2+N/4。其中,N为该级DFT运算的点数,各级使用的移位寄存器深度逐级递减,从而大大降低了寄存器的使用数量。

此外,由于各级结构固定,所以大点数FFT只是小点数FFT基础上级数的增加,而且由于移位寄存器的输出相对于RAM而言不需要复杂的地址控制,所以这种结构的FFT处理器具有非常好的可扩展性。比如需要实现512点的FFT,只需要在256点的基础上增加一级即可。

3 具体模块的设计

3.1 控制与地址产生模块

由于两路数据同时输入,为了防止发生两路数据间的串扰,对数据的控制显得极其关键。从上面的算法结构分析中知道,由于后级的DFT运算点数是前一级的一半,所以后一级的开关转换周期也是前一级的一半,基于这种关系,可以使用一个8位计数器的每一位状态来对各级开关进行控制。最高位控制第一级,同时由于上一级数据进入下一级需要一个时钟,所以下一级的开关转换时刻要比上一级延迟一个时钟周期。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码