多功能数据采集处理系统实现

A/D电路

高速A/D芯片的输入端通常采用差分输入,这种方式有以下优点:差分特性对来自电源和其他电路的外部共模噪声源具有抑制作用;能够抵消偶次谐波;每个差分输入所需电压摆幅仅为单端输入时的50%,可以降低对电源的要求。

本设计中运放采用的是ADI公司的AD8138,体积非常小巧,使得A/D芯片与信号输入点的距离可以很近,大大减少了外界噪声的影响,是理想的驱动芯片。单端转差分器件选用Mini-Circuits 公司的宽带变压器ADT1-1WT,其工作频带为0.4~800MHz,配合简单的电阻网络及滤波电容就可以完成设计任务了。

LTC2260的工作时钟由FPGA提供,输出1.8V的并行数据到FPGA进行处理,FPGA采用2.5V的I/O电压。

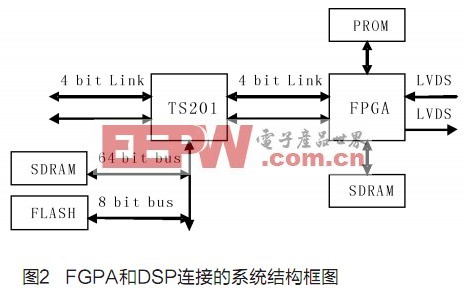

FPGA和DSP的设计

本系统采用松耦合结构设计,FPGA和DSP都有其各自独立的存储器,DSP和FPGA之间通过LINK进行互连,DSP与FPGA之间通信通过编写FPGA仿TS201 LINK逻辑完成,DSP还可通过LINK与外部交换数据,系统结构框图如图2所示。这种连接方式的优点在于:

(1) DSP和FPGA片间数据交换数据率更高,最高可达4GB/s;

(2) DSP和FGPA可以同时访问各自的外部存储器,系统总的存储带宽较大;

(3) DSP和FPGA访问外部存储器的同时可以通过LINK链路进行数传通信;

(4) 系统硬件连线相对独立,易实现。

FPGA接口设计

FPGA主要提供3个逻辑接口,分别为与DSP的LINK接口、外部存储器SDRAM的接口以及系统的输入输出接口。与DSP的LINK接口采用IP核设计实现,接口能够稳定工作在500MHz速度上,为FPGA和DSP之间提供4GB/s的数据传输能力。

FPGA到SDRAM接口逻辑自行设计,与DSP外部存储器相同采用4片K4S511632M 构成64bit的256MB存储空间。接口工作在80MHz时钟频率,数据率为640MB/s。

FPGA的输入输出接口连接到系统外,因此采用LVDS协议来保证信号的稳定、准确传输,双向各提供32bit数据宽度,采用250MHz的板间传输频率,可以提供2GB/s的传输能力。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码