基于Taylor级数近似补偿的改进数控振荡器实现

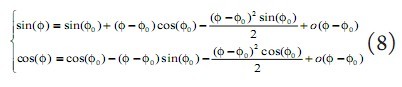

二阶泰勒补偿实现的原理如下:假设相位累加器输出的相角 为N bits的,把相角 分成三部分,即N=j+k+2。由于CORDIC能计算相角的范围为[-99.9°, 99.9°]之间,这是由CORDIC算法本身所决定的,这样就必须通过三角关系把输入相角转换到[-99.9°, 99.9°]之间,本文利用输入相角的高两位来判断相角的转换。然后再把接下的(N-2)bits的数据分成j bits和k bits两部分,中间j bits作为CORDIC的输入相角 ,后k bits作为后续二阶泰勒补偿模块的输入数据。在这里并没有把整个(N-2)bits的角度 作为CORDIC的输入,而是只取了前j bits,这样就会很大程度的降低模块的占用资源,同时,减少输入数据的位宽就会减少迭代的次数。由于这样只取 的高 1位作为CORDIC的输入,这样产生的截断舍入误差会影响到整个数控振荡器的SFDR,为了补偿这部分的损失,本文采取二阶泰勒级数来补偿这部分损失,对于低k bits的角度(-)用来作为二阶泰勒级数补偿的输入相角。利用二阶泰勒级数补偿(公式8),可以计算出比较准确的正余弦值。

仿真结果

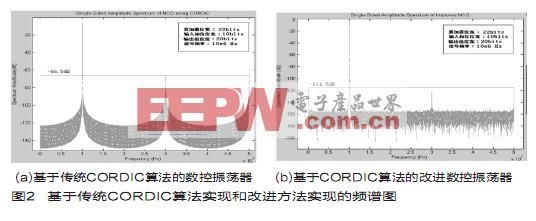

为了验证结果有可比性,验证性能时采用无杂散动态范围值(SFDR)这一公认指标进行衡量。在频域中,SFDR是衡量一个信号失真特性的有效方法,SFDR为定义在一定频率范围内的信号与第二大频率成分的功率差。在验证性能时,用Matlab对基于CORDIC算法的改进数控振荡器进行仿真,在仿真时采取了定点化仿真,输入相位位数为22bits,输出的正余弦值的位宽为20bits,对于本文提的方法的具体参数设定如下:CORDIC的输入位宽k=10bits,累加器位宽N=22bits,采样频率,输出正余弦信号的频率,仿真的结果如图2(b)所示,从图中可以看出本文提出的方法的SFDR值可以达到114.5dB,输出信号的频谱能量主要集中在10MHz附近,但第二大频率成分的尖峰出现0Hz附近,这个尖峰是未补偿尽残余杂散频谱,它与主频谱幅度相差近115dB,对数控振荡器的性能影响很小。并且,随着累加器位宽和输出信号位宽的增加,数控振荡器的SFDR值会进一步提高,本文的实现方法在输出正余弦值位宽为24bits时,它的SFDR值可以达到134dB。

图2(a)所示的是基于传统CORDIC算法实现的数控振荡器,它的SFDR值达到66.5dB。从图2可以看出改进方法提高SFDR值近48dB。本文的改进方法与其他的实现方法的性能比较见表1,从表中可以看出本文提出的改进方法比参考文献提出的实现方法的输出信号SFDR值都要高,所以,本文提出的方法输出信号频谱的纯度要优于其他方法。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码