基于ACE约束的S-IRA编译码器设计

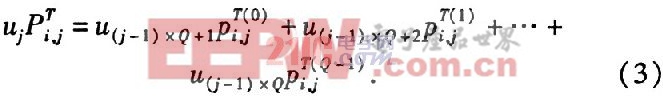

假设v=uPT,v=(v1,v2,…,vM),其中,有下式成立:

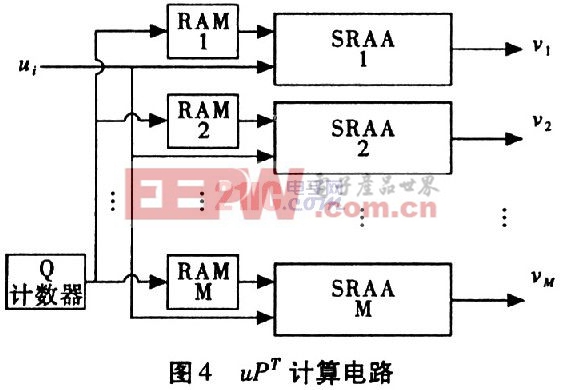

由(2)式以及(3)式,计算vi的电路如下:

图中的第i个RAM储存对应循环置换矩阵的参数,即的第一行“1”元素的位置,因此每个RAM存储K个“1”元素位置。编码时,每输入Q个信息位,SRAA电路便从RAM中读入循环置换矩阵的参数。

交织器使用一段RAM存储交织顺序,并按存储的顺序读出SRAA中运算结果v,即完成交织。

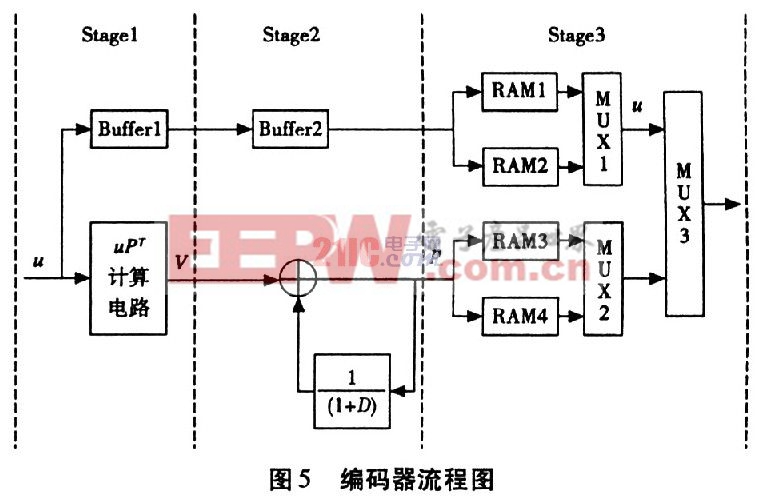

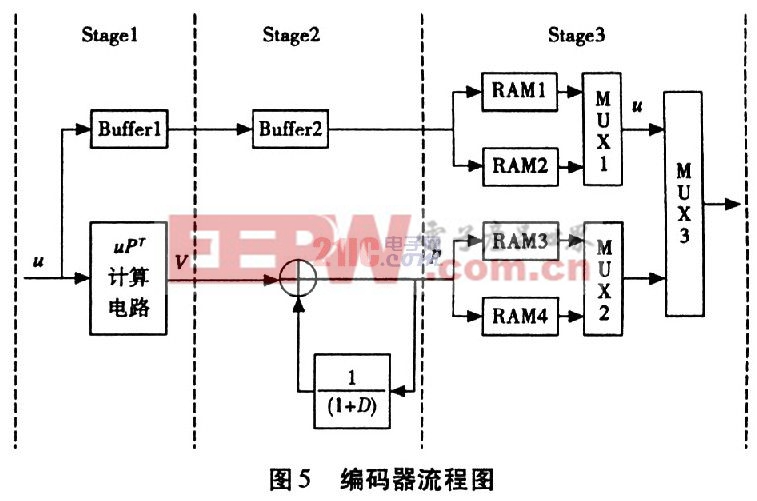

基于上面的SRAA计算电路本文提出了图5所示的编码器结构。

为了使编码连续进行,在交织器之后以及编码器输出端使用乒乓RAM,如图5中的RAMl和RAM2,以及RAM3和编码流程可分为三步:

Stagel:串行输入信息u,每个输入的信息ui分成两路,一路依次存入Bufferl缓存器,另一路输入uPT计算电路,计算结果v保存在SRAA电路的寄存器中。

Stage2:从Buffer2中将信息位依次读至RAMl、RAM2,Bufferl中的信息依次读至Buffer2,而Bufferl中继续存入新的信息位。交织器将uPT计算电路的计算结果按交织顺序读至累加器,并将产生的校验位输入RAM3、RAM4。

Stage3:将RAMl或RAM2中的信息位u以及RAM3或RAM4中的校验位p依次读出,完成码字的串行输出。

2 译码器设计

译码方面采用了LMMSA算法。为了便于硬件的并行处理,本文采用LMMSA译码算法,在分层上保证每层的列重至多为1。对于前面所提到的S-IRA码,则可以对校验矩阵按照每行为一层进行分层,即从列上看每一层只有一个循环位移矩阵或全零矩阵。

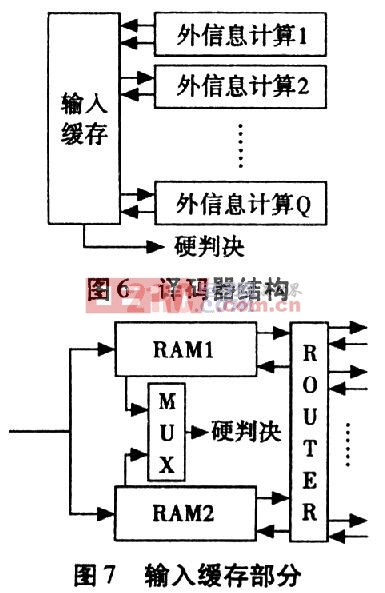

针对上面提到的S-IRA码本文提出了如图6所示的译码器结构。

其中Q=36,M=14,K=14,设计成输入缓存部分以及外信息计算部分。其中外信息计算部分每次计算一层的校验位,因此并行度为Q=36,将接收到的通过信道串行输入的每个信息比特的接收值量化成7位定点数,为了让译码器能连续地接收通过信道传递的信息,输入缓存部分也采用乒乓RAM的形式。由于外信息计算部分的并行度为Q=36,因此输入缓存部分与下一级之间的每次输出/输出均为Q×7位。由于RAMl、RAM2储存外信息值,因此直接对其中的外信息进行硬判决。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码