NiosII的I2C控制IP及其在成像系统中的应用

摘要:详细介绍一种I2C控制IP的工作原理及其可编程寄存器,给出该IP在CMOS数字成像中的应用实例。该实例基于可编程片上系统(SOPC)技术设计,在NioslI IDE中通过编写程序来实现系统功能,并通过QuartusII软件自带的SignaITapII进行验证。结果表明,在CMOS成像领域选用该IP核,系统能充分利用SOPC技术的优势,具有扩展性好、控制灵活、开发周期短等特点。

关键词:SOPC;I2C控制IP;CMOS

1 IP的硬件结构及寄存器

1.1 IP硬件结构

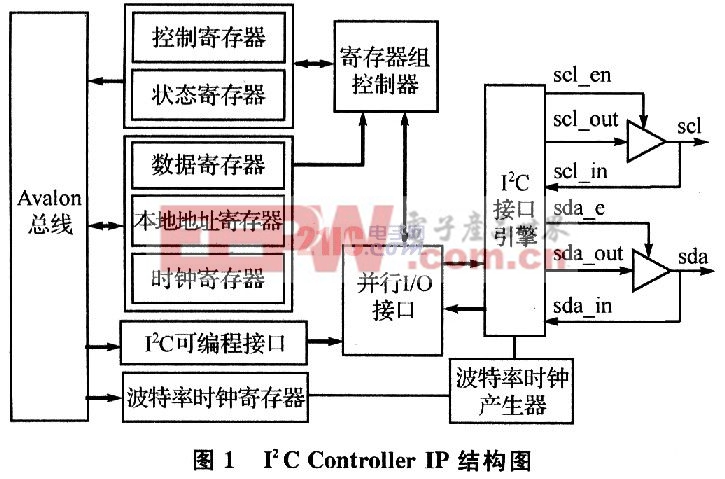

IP内部结构如图1所示。主要由波特率时钟寄存器、寄存器组控制器、并行I/O接口、I2C可编程接口、I2C接口引擎5个模块组成。波特率时钟产生器用来产生I2C IP工作的基本时钟频率;寄存器组控制器用来对寄存器进行设置,设置数据通过并行I/O接口传送到该模块中;并行I/0接口模块用来处理可编程接口模块传送过来的命令;I2C可编程接口模块用来设置IP各个寄存器的地址;I2C接口引擎模块执行I2C总线上数据的传输。

1.2 寄存器结构

I2C控制IP主要由6个寄存器构成,如表1所列。通过对寄存器的读写可以方便地控制I2C总线数据的传输,从而实现NioslI处理器与设备之间的通信。数据寄存器用来存放I2C总线上要传送的数据;波特率产生模块,波特率时钟寄存器和时钟寄存器共同决定I2C总线上SCL的频率。SCL的计算公式为 。其中System_clk是系统时钟;Value是时钟寄存器的值;divider是波特率时钟寄存器的值所对应的分频数(寄存器的值与分频数相差为1,如寄存器设置为O,则分频数为1;寄存器设置为1,则分频数值为2)。本地地址寄存器、控制寄存器、状态寄存器的详细介绍略――编者注。

。其中System_clk是系统时钟;Value是时钟寄存器的值;divider是波特率时钟寄存器的值所对应的分频数(寄存器的值与分频数相差为1,如寄存器设置为O,则分频数为1;寄存器设置为1,则分频数值为2)。本地地址寄存器、控制寄存器、状态寄存器的详细介绍略――编者注。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码