基于Compact PCI体系的高性能监测测向处理平台研究

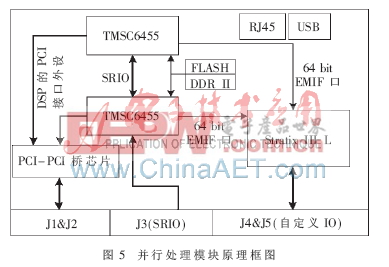

主处理平台的计算能力往往构成了获取宽带信号时频域完整信息的瓶颈。本文针对一体化设计的具体需求探讨了一种紧耦合和支持灵活配置的并行处理硬件架构来解决这一问题[3]。信号处理不同模块有不同的运算特点,设计过程中,不同的模块需要选择在不同的器件中完成[7]。FPGA设置灵活,但是主频很难做高,通常只有几百MHz,这与DSP的几千MHz甚至于GHz相去甚远。因而,对复杂的运算和协议分析适合采用DSP处理,而FPGA则偏重于计算量大、运算结构简单的并行处理,在诸如数字下变频(DDC)、匹配滤波器、FFT的设计中具有更好的性能,而且开发方便。同时,要充分体现软件无线电的思想,达到通用性与一体化的要求,可重配置技术的突破是必须完成的任务。FPGA具有的硬件可重构性是GPP、DSP所没有的功能,所以本文采用基于大规模FPGA+高性能DSP的主处理平台设计方案也是保证系统结构具有可重配置特性的前提。同时,为了保障与本总线式结构平台的各个组成部分有好的通联性,并考虑到系统性能和处理能力的可扩展性,本模块采用CPCI作为互联控制总线,设计遵循CPCI 6U规范,并预留有SRIO(J3)、高速自定义IO(J4、J5)作为模块之间或板级芯片之间高速数据流共享和协同处理的通道。该并行处理模块硬件功能相对独立,可方便功能需要的裁剪定制。同时,这些特征也决定了硬件平台具有较长的使用周期,节约了研发经费。并行处理模块原理框图如图5所示。

本并行处理模块采用TI全新高性能1.2 GHz单核DSP TMS320C6455作为并行处理的核心,为同时执行多通道处理任务和应对同时执行多个软件的高强度、高性能应用提供资源。C6455在统一器件上完美结合了高带宽外设集成(千兆以太网MAC)、Serial RapidIO(SRIO)、运行速率553 MHz的DDR2存储器接口以及更大的存储器(L2存储器达 2 MB)。这些为提高常用算法的处理效率、提高系统扩展能力提供了原始支撑,满足了一体化的高性能设计要求。

本文基于最新技术,就高性能监测测向处理平台设计所需的高速数据采集、数据传输、实时处理等核心技术进行了研究,实现了通用系统的多功能性与专用系统的针对性的有机结合,在一体化集成与应用研究方面具有创新性。在充分体现资源裕量设计的基础上,该平台具有很好的实时处理分析和信息综合性能,可以满足多种应用背景和不同技术指标的需求,在工作方式上具有高度的灵活性和适应性。

参考文献

[1] 刘小刚,张圆圆,杨汝良.基于CPCI总线的高速大容量通用信号处理机[J].数据采集与处理,2008,23(3):347-351.

[2] 向新.软件无线电原理与技术[M].陕西:西安电子科技大学出版社,2008.

[3] 朱然刚,钟子发,许阳明,等.宽带并行处理技术的应用研究[J].现代防御技术,2009,37(2):91-94.

[4] 郭四稳,古乐野.多通道大容量高速数据采集系统[J].四川大学学报,2001,38(1):29-32.

[5] 贾金锁,高梅国,韩月秋.大容量高速数据采集系统的设计[J].电讯技术,2003(6):60-63.

[6] 黄春行.超高速数据采集系统的时序设计与信号完整性分析[D].南京理工大学硕士学位论文,2004.

[7] 曾义芳.DSP开发应用技术[M].北京:北京航空航天大学出版社,2008.

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码