远程心电医疗信号监测系统设计

NiosⅡ处理器采用Avalon交换式总线,该总线是Altera开发的一种专用的内部连线技术。Avalon交换式总线由SOPC Builder自动生成,是一种用于系统处理器、内部模块以及外设之间的内联总线。Avalon交换式总线使用最少的逻辑资源来支持数据总线的复用、地址译码、等待周期的产生、外设的地址对齐、中断优先级的指定以及高级的交换式总线传输。

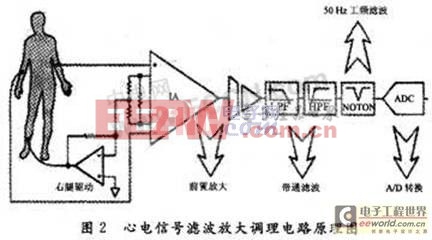

3.2 心电信号采集调理模块设计

对ECG信号采集采用模块化的设计方式,主要由前端的导联传感器、信号滤波放大调理电路和A/D采样电路组成。人体心电信号的主要频率范围为0.05~100 Hz,幅度约为0~4 mV,信号十分微弱。同时心电信号中通常混杂有其他生物电信号,加之体外以50 Hz工频干扰为主的电磁场干扰,使得心电噪声背景较强,测量条件比较复杂。为了不失真地检测出有临床价值的心电信号,信号滤波与放大调理部分主要由一下几个电路组成:前置放大电路、高低通滤波电路、陷波电路与A/D转换电路,电路原理图如图2所示。

首先心电导联采集过来的微弱心电信号通过前置放大电路进行放大,此部分包括右腿驱动以抑制共模干扰、屏蔽线驱动以消除引线干扰,增益设成10倍左右。设计前置放大采用美国模拟器件公司生产的医用放大器AD620。AD620由传统的三运算放大器发展而成,为同相并联差动放大器的集成。其具有电源范围宽(±2.3~±18 V),设计体积小,功耗低(最大供电电流仅1.3 mA)的特点,因而适用于低电压、低功耗的应用场合。此外还具有有较高的共模抑制比,温度稳定性好,放大频带宽,噪声系数小等优点。放大后的信号经滤波、50 Hz陷波处理后再进行二次放大,后级增益设成100倍左右。由于ECG信号幅度最大就几mV,而A/D转换中输入信号的幅度要求在1 V以上,所以总增益设成1 000倍左右。其中,滤波采用压控电压源二阶高(低)通滤波电路,用于消除0.05~100 Hz频带以外的肌电等干扰信号,工频中的其余高次谐波也可被滤除掉。同时,采用有源双T带阻滤波电路进一步抑制50 Hz工频干扰。

A/D采样芯片采用TI公司的8位串行芯片TLC549,该芯片采用SPI接口,仅用三条线即可实现采集控制和数据传输;具有4 MHz的片内系统时钟和软、硬件控制电路,转换时间小于17μs,采样速率达40kS/s;采用差分基准电压技术这个特性,TLC549可能测量到的最小量值达1 000 mV/256,也就是说0~1 V信号不经放大也可以得到8位的分辨率。

3.3 数据采集控制器设计

为了得到经过前端TLC549芯片转换的心电信号,必须设计一个数据采集控制器,实现对AD芯片的控制与数字化心电数据的获取。该控制器根据TLC549芯片的工作时序与后端数据处理的需要,采用VerilogHDL自行设计。该控制器具有多路采集的特点。

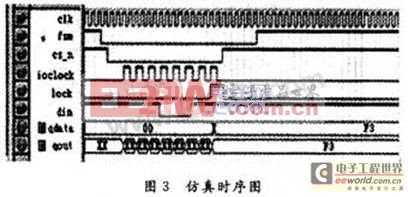

在自TLC549的I/O CLOCK端输入8个外部时钟信号期间需要完成以下工作:读入前次A/D转换结果;对本次转换的输入模拟信号采样并保持;启动本次A/D转换。则一路采集时间为:0.5μs×(3+8×2+1)=10μs,而芯片转换时间小于17μs,则整个过程时间花费为27μs。为了有效的利用该控制器,在一路A/D转换期间,同时进行另外一路A/D采样,这样就可以在40μs时间内完成对四路信号的采集,大大提高了工作效率。同时,设计中还加入了一个FSM信号来控制采样时间,从而适应不同频率信号的采样频率。AD芯片的时序仿真图如图3所示。

Din为采集数据的串行输入,时钟由系统时钟通过分频系数得到。设计中,设置了fsm作为采样控制时钟,这样可以根据需要来调整采样速率。由于进行一次AD采样的时间很短,无论采用查询还是中断直接读取都是不现实的,这就需要利用缓冲设计,通过把N次转换的数据暂存在缓冲存储器中来降低中断次数。为了取得连续和正确的采集数据,实现无缝缓冲,鉴于FPGA设计的灵活性,本设计采用了双缓冲存储的乒乓操作结构。本设计通过将AD采样时序控制器交替存储在两个512 B的双口RAM(DPRAM)中实现数据的缓存,当其中一个DPRAM1存储满后即转为存储到另一个DPRAM2中并产生一次中断,这样在控制器写数据到DPRAM2中时系统将有非常充足的时间将DPRAM1中的数据取出。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码