基于ADV7183B的视频解码系统的设计

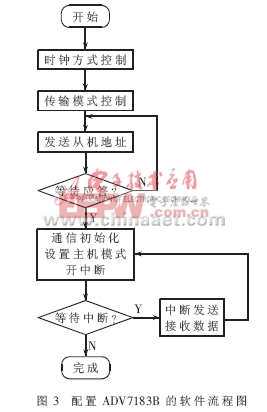

首先,初始化时钟和传输模式,使MSP430F169工作在所需的模式下;其次,初始化I2C功能,使其准备将从机地址发送到I2C总线上,等待总线上的从机应答,若无应答则重复发送,若有应答则通信初始化并开中断,发送所需配置的寄存器地址和数据[10-11]。需要注意的是,在每次发送数据前都要初始化主机模式和传输模式的设置,因为每次发送完数据后,这两个标志位都会被自动清零。

为了使ADV7183B正常工作,几个主要寄存器的配置内容如下:

(1)输入选择寄存器INSEL,地址为0x00。根据外部接口情况,用户可通过设置这个寄存器选择模拟视频源的输入通道和输入模式,即选择通过CVBS、S-Video或YPrPb输入。在该系统中,CVBS信号由AIN5输入,则寄存器内容设置为0x04;S-Video信号的Y接入AIN1,C接入AIN4,则寄存器内容设置为0x06;YPrPb信号的Y接入AIN2,Pb接入AIN3,Pr接入AIN6,则寄存器内容设置为0x0A。同时,未连接的其他输入通道管脚必须接地。

(2)输出模式选择寄存器OF_SEL,地址0x03。通过设置此寄存器,用户可控制输出数据为8 bit或16 bit。不过,此寄存器必须和像素时钟寄存器(LLC_PAD_SEL,地址0x8F)一起设置。当输出16 bit数据时,像素时钟为13.5 MHz;而当输出8 bit数据时,像素时钟则为27 MHz(默认设置)。所以程序中,8 bit输出时,0x03设置为0x0C,0x8F设置为0x00;16 bit输出时,0x03设置为0x00,0x8F设置为0x50。

(3)ADC低功耗控制寄存器,地址0x3A。这个寄存器可以选择ADC的工作个数。在CVBS模式下,ADC1和ADC2低功耗,即不工作;在S-Video模式下,ADC2低功耗;而在YPbPr模式下,3个ADC全部工作。同时,还需要配置相应的寄存器地址是0xC3和0xC4,这2个寄存器设置了3个ADC所连接到的管脚。根据外部的模拟输入源,CVBS模式时,ADC0连接AIN5,则0xC3设置为0x05,0xC4设置为0x80;S-Video模式时,ADC0连接AIN1,ADC1连接AIN4,则0xC3设置为0x41,0xC4设置为0x80;YPrPb模式时,ADC0连接AIN2,ADC1连接AIN3,ADC2连接AIN6,则0xC3设置为0x32,0xC4设置为0x86。

(4)行、场同步信号的相关寄存器,一般采用默认设置即可。

3 实验结果

在系统调试时,采用了一个彩色数字摄像头作为视频输入源,即输入CVBS格式的模拟视频信号,通过逻辑分析仪捕获输出管脚的波形,观测相应的信号和输出数据。通过不断修改程序,最终实现视频图像的采集、显示。图4是通过MSP430F169设置ADV7183B的输出模式选择寄存器的波形。可见,时序满足标准的I2C总线协议的传输时序:起始―从器件地址(0x40)―应答―从器件的寄存器地址(0x03)―应答―写数据(0x0C)―应答―结束。图5和图6是解码后的视频数据。在图5中,根据固定前缀FF 00 00 F1可知,F1(1111 0001)所包含的信息是表示行由0跳变为1,场由0跳变为1,传输数据进入的是行和场的消隐期。而图6中,由固定前缀FF 00 00 80可知,80(1000 0000)所包含的信息是表示行由1跳变为0,场由1跳变为0,传输数据进入的是行和场的有效期。由此表明,视频解码系统输出的视频数据符合CCIR656标准,达到了设计要求。

综上所述,本视频解码系统利用MSP430F169进行解码芯片ADV7183B的设置,具有低功耗、小巧灵活等特点。同时,作为视频输入前端,将彩色摄像头的模拟视频源转换成16 bit的YCrCb型4:2:2数字视频数据,并进行格式转换、滤波等处理后,通过DVI接口在CRT上清晰显示,达到了设计要求,能够为相应的视频后处理设备(如DSP、FPGA等)提供良好的数字视频数据。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码