基于ARM和FPGA的微加速度计数据采集系统设计

2.3 Altera-FPGA与ARM处理器

该系统的FPGA采用Altera FPGA公司的CycloneⅡ系列的EP2C35实现,EP2C35提供多达33 216个逻辑单元(LE),35个18×18位乘法器483 840 b的内部RAM块,专用外部存储器接口电路,4个锁相环(PLL)和高速差分I/O等功能。

该系统中采用的ARM处理器是Philips公司的LPC2210,是基于一个支持实时仿真和嵌入式跟踪的16/32位ARM7TDMI-S CPU的微控制器。 LPC2210的144脚封装、极低的功耗、两个32位定时器、八路lO位ADC,PWM输出以及多达九个外部中断使其特别适用于工业控制、医疗系统、访问控制和电子收款机等。通过配置,LPC2210最多可提供76个GPIO。由于内置了宽范围的串行通信接口,其也非常适合于通信网关、协议转换器以及其他各种类型的应用。

3 采集系统整体实施方案

3.1 FPGA控制A/D芯片进行加速度计数据采集

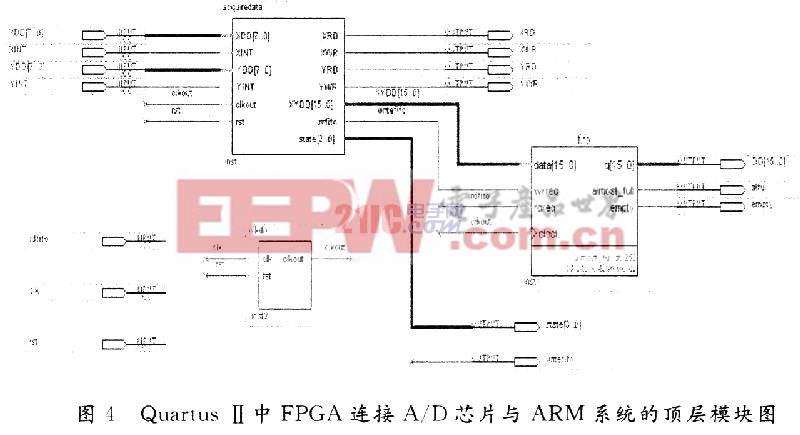

该加速度计是利用两路模拟电压输出来反映加速度值的大小,当加速度值为O时输出电压为1.50 V,电压输出灵敏度为150 mV/g,A/D转换器模拟输入电压范围为VCC±0.1 V,低于VREF- +(1/2)LSB或高于VREF+ -(1/2)LSB的模拟输入电压分别转换为00000000或1111111,系统中所加电压分别为VCC=VREF+=5 V,VREF-=GND=O V。TLC0820可通过MODE的设置工作在只读和读写两种方式。当MODE为低时,转换器为只读方式。在这种方式中,作为输出,且作为准备输出端;同时。当为低时,亦为低,表明器件忙,转换器在的下降沿开始转换,经过不到2.5μs转换完成,此时下降.为高阻,数据输出也由高阻变为有效的数据端,当数据读出后,变高,返回高,数据输出端返回到高阻态。当MODE为高时,转换器为读/写方式,作为写输出端。当和为低时,转换器开始测量输入信号,大约600 ns后返回高,转换器完成转换,在读写方式中,在上升沿开始转换。该实验采用读写方式来控制A/D芯片来读取加速度计的值,所需的控制信号由FPGA输出,相关的逻辑控制采用Verilog硬件描述语言进行编写,图4为QuartusⅡ中FPGA连接A/D芯片与ARM系统的顶层模块图。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码