TMS320C542在脱机视频编/解码系统中的应用

2.4 图象数据存储SRAM

为了实现数据传输的流速控制,需要存储器缓冲数据。同时,要实现图象冻结和其它一些处理功能,也同样需要足够的存储空间。本系统选择了128K×16bit的高速SRAM来扩展C542有限的存储空间。C542的内部RAM占据了地址从0000~27FFh的数据区,8000~0FFFFh的的数据区已经分配给了EPROM放置程序代码,最后只有2800~7FFFh的地址可以给SRAM使用。有一种扩展SRAM访问地址线的方案是采用两次寻址方法。第一次先给出部分地址并缓存下来,此时不访问数据;在第二次访问时,给出余下的地址数据,然后利用拼接的总地址来访问数据。

由于图象数据是数据流,它在SRAM中的存放和读取都是地址顺序递增的。依据这一特点,本系统设计了一种新的SRAM地址线扩展方法。该方法将每32个16位字图象数据划分为一次数据操作的最小单元组。这32个字数据在SRAM中存放地址的高12位是一样的,这高12位地址用DSP的低12位地址线选择。而SRAM的低5位地址用一个5位二进制计数器自动递增生成,即每访问一次高12位地址,低位地址自动增1.这样,实际只用了DSP的12根地址线,就可以高效地访问SRAM的所有存储空间。最后,DSP地址线的高四位A15~12应该在0011~0111之间选择两个值,一个用来片选SRAM,一个用来复位计数器。

2.5 数据通信高速串口

本系统直接利用C542的缓冲串口BSP作为系统开放给用户的通信接口。该接口的数据速率最高可以达到40Mbps,数据包的长度可以在8位、10位、12位和16位之中选择。BSP串口的接收部分BSPR操作在被动方式下,伴随接收数据的时钟和帧同步信号应该由外部提供。BSP串口的发送部分BSPX既可以工作在主动模式下,其数据时钟和帧同步由DSP内部提供。BSPX也可以工作在被动模式,数据时钟和帧同步时钟由外部输入。BSP的缓冲区数据自动发送和接收功能,也简化了DSP的处理工作。本系统在DSP的BSP串口基础上增加了接口驱动,构成了系统的通信接口。

3 DSP部分的系统设计

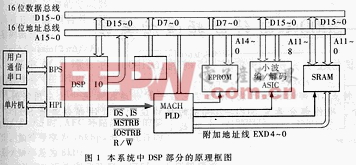

图1是本脱机视频编/解码系统的核心DSP部分的构成原理图,其中DSP的缓冲串口DSP单独构成了用户通信串口,DSP的HPI接口实现了DSP和低速控制单片机之间的通信。剩下与DSP的IO接口相连接的外围是上电复位SRC数据逻辑、程序加载EPROM、视频图象编/解码ASIC和图象数据存储SRAM。EPROM和SRAM作为DSP扩展的数据存储区来处理,SRC数据逻辑和视频编/解码ASIC作为DSP的IO端口来访问。从程序指令角度讲,数据存储区的访问操作应该使用DSP的数据访问指令,例如LD、ST、MVDD等等,而IO端口的访问要使用DSP的IO端口访问指令PORTR和PORTW。

DSP的IO接口的16位数据线和16位地址线构成外围器件的数据总线和地址总线。小规模的MACH可编程逻辑器件被用于设计IO外围器件的访问控制逻辑。MACH产生的每个器件的片选和读写信号由它与DSP的关系、它的寻址范围以及管脚信号特性决定。例如程序下载EPROM是DSP扩展的数据区,寻址范围8000~0FFFFh,如果它的片选信号是高电平有效,EPROM片选逻辑为:

CS-EPROM=(!DS)A15

当DSP访问数据区时,DS有效,为低电平,并且当地址线的最高位A15为1时,CS_EPROM信号有效,EPROM被选通。此外,用于SRAM访问地址自动递增的二进制五位计数器也由MACH可编程逻辑器件实现,构造出了附加的5条地址线。

通过利用DSP芯片TMS320C542所具有的DSP和HPI接口功能,并结合MACH可编程逻辑芯片扩展DSP的IO接口功能,从而实现了脱机视频芯片扩展DSP的IO接口功能,从而实现了脱机逻辑芯片扩展DSP的IO接口功能,从而实现了脱机视频图象编/解码系统的控制核心的设计。通过实际的调试,DSP能够在上电复位时正确地从EPROM下载程序代码并运行,DSP可以正确地访问视频编/解码ASIC和数据存储SRAM,DSP与单片机的命令数据交换和串口数据的传输都能正常实现。这个结构合理、布局紧凑的硬件设计为进一步的软件开发提供了方便。DSP对外围数据访问的指令代码,特别是对SRAM的访问操作,简单高效,这为DSP程序软件中其它图象实时控制算法节省了宝贵的指令周期资源。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码