机载TM总线接口设计方案

2.2.2 TIU的设计原理

从数据信号流程方面来说:接收数据时,TM总线上的输入信号经过译码转换进入寄存器,在这里完成数据串/并格式转换,进行奇偶校验检查,检查后如果正确,则通过地址比较逻辑,进行命令译码,按照所给出的命令送入所定义的不同作用的寄存器中。

TIU执行控制命令的过程如下:TIU链路层状态机控制命令的接收,核心状态机执行该命令,并把待传送的应答传送至移位寄存器中,再由TIU链路层状态机控制应答传送。由软件实现的命令其执行过程是核心状态机将该命令传送至输入接口缓冲器并产生中断信号,模块中的CPU响应中断,从输入接口缓冲器中读取命令,进行测试操作和模块维护操作,并把结果写入状态寄存器或输入缓冲器,然后TM总线主控制器取走该测试结果。

2.3 TM总线状态机设计

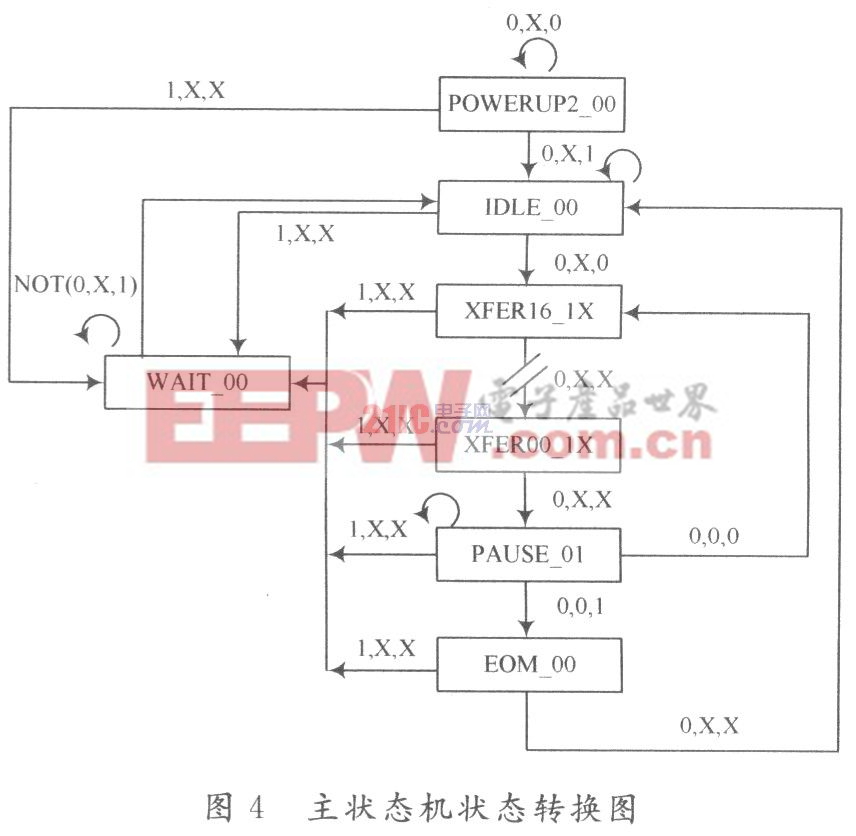

TM总线协议规定其链路层状态机分为主从两个状态机,由于TIU不存在同时既做主又做从的工作模式,因此可以把主/从两个状态机合为一个。通过控制使TIU工作在主/从两种模式下,主方式下的TIU发送命令,从方式的TIU接收并执行命令。图4为主状态机状态转换图。

在TM-BUS主状态机状态标记中,最后两位表示在该状态下MCTL和MMD的值,状态转换的条件由状态变量M1,M2,M3表示。图4中所标的转换条件为[M1,M2,M3]取值。POWERUP2_00为上电后或复位后的状态;XFERl6_1X~XFER00_1X为数据传送状态;WAIT_00为出错状态,该状态结束的条件是MCTL与MMD发生传输冲突消失且消息传送结束;在PAUSE_01状态下插入等待;EOM_00为消息传送的起始和结束状态。主/从两个状态机合为一个状态机后,MCS和主权控制状态机控制作何种状态机运行[M1,M2,M3]控制主状态机的状态转换,从状态机的状态转换由MCTL和MMD控制。

2.4 USB接口设计

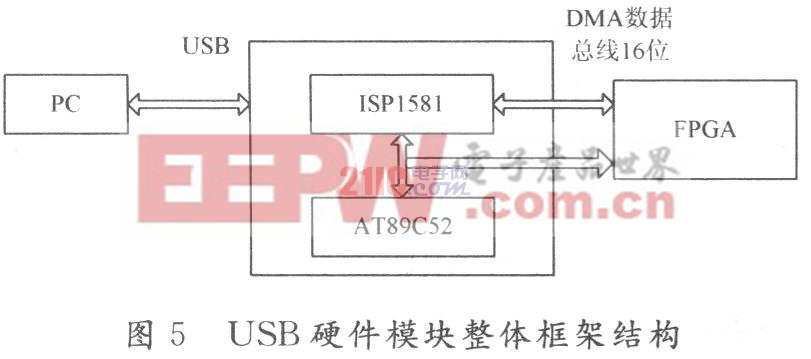

USB接口芯片采用了ISP1581。ISP1581是Phil-lps 公司提 不应求的高速USB接口芯片,符合USB2.0规范。它的内部集成了数据收发器、串行接口引擎(SIE)、并行接口引擎(PIE)、FIFO存储器(8 KB)、存储管理单元(MMU)、微控制器接口和DMA(直接内存访问)管理器。外部电路接口简单,因ISP1581内部不带有微控制器,需外接。本文的微控制器采用AT89C52单片机。USB硬件模块主要包括ISP1581,AT89C52,总体框架结构如图5所示。

ISP1581通过16位数据总线与FPGA相连,AT89C52负责控制数据的DMA传输。ISP1581与微控制器的通信通过一个高速(15 MB/s或15 Mword/s)的通用并行接口AD[7:O]实现,并具有高速DMA接口。

2.4.1 USB接收数据模块实现

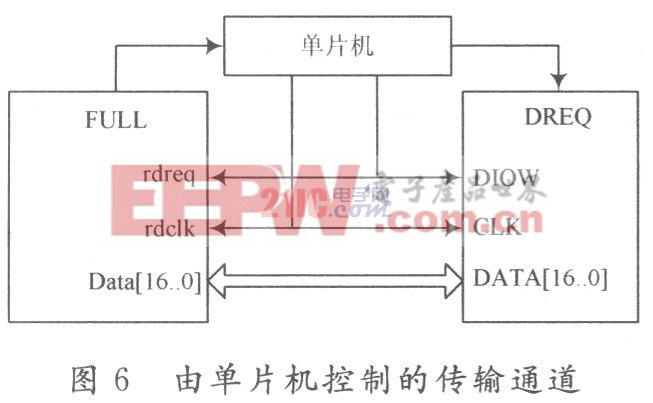

本文采用的USB器件是带有DMA控制器的ISP1581,为了简化电路,采用ISP1581的DMA主控制器方式。如图6所示,当FPGA的FIFO满标志为1时,单片机给ISP1581发送请求有效信号、写信号和写周期信号,给FIFO发送读请求信号和读周期信号,当读出的数据达到预定的数目时,单片机把ISP1581请求信号设置为无效,等待下一组存储数据。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码