用FPGA实现音频采样率的转换

显然,用FPGA实现音频频率的采样率转换器存在以下问题:

1. 算法问题:

a. 可能的最高信噪比

b. 原始信号所载信息的可能最小变化

c. 算法的有效描述,因为FPGA中的资源消耗在很大程度上取决于描述的质量

d. 量化

2. 实现问题:

a. 逻辑正确的算法实现

b. FPGA资源限制

c. 速度优化实现

d. 延迟

转换需要较高的时钟速度,因为具体实现取决于对转换信号的足够过采样。FPGA系统时钟频率与待转换信号的频率差异必须相应较大。

FDA 工具可帮助生成和验证各种FIR和IIR滤波器。该工具是Simulink信号处理工具箱的组成部分,Synplify DSP就是使用此工具箱实现滤波器结构

对于CD质量的音频信号,还要求信噪比不得低于100dB。专业应用甚至需要大于 120dB的音频信号。就信号质量而言,其他低频信号(如控制电路算法)远不如音频信号那样苛刻。

算法

多相FIR滤波器结构需要转换采样率(异步重采样)。算法包括两步,第一步是频率过采样,第二步是线性插值,这是从给定频率生成不同频率时需要的。这两个频率相互异步。

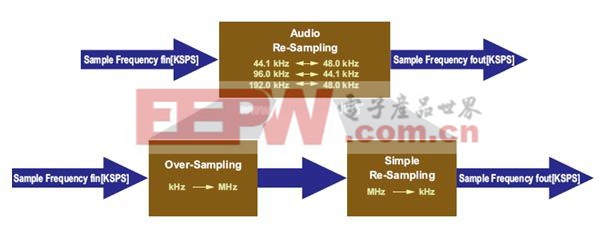

以单步方式进行信号重采样所需资源较多,因为滤波器会较复杂。这种实现需要数百万次乘法运算。这样的描述效率很低的,应当加以避免。如果线性插值在第二步实现,那么结构就会简单得多(图3)。

图3:分两步实现采样率转换器(一、过采样;二、线性插值)以提高效率。

高效地描述过采样(第一步)是让 FPGA实现节省资源的唯一方法。如果用若干级联级而非单一运算步骤来实现这部分电路,所需运算数量就会大大减少。

在算法实现时,必须确定执行运算的目标架构(DSP或FPGA)。与具有固定架构的数字信号处理器不同,FPGA可实现任何架构。不过,当实现大量单独的乘法运算时,FPGA最终会受到器件尺寸的限制。

所需乘法器的数量将随着滤波器抽头的增加而增加。每个抽头都需要使用一个DSP模块或乘法器。当级联重采样电路时,各滤波器必须执行复杂程度很低的功能。从理论上讲,单独的级越多,滤波器的实现就越好。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码