通过USB接口实现FPGA的SelectMap配置

3.配置时序的发生

配置数据需要在配置时序的配合下写入 FPGA[5]。GPIF是一个可编程的状态机,它可以采集 5个输入引脚(RDY)的状态,并通过 5个输出引脚(CTL)对外产生任意时序,因此可用来产生 FPGA的配置时序。表 1说明了 FPGA在 SelectMap模式下各配置引脚的作用[5],如图 1所示,CCLK连接 EZ-USB提供的界面时钟 IFCLK,D[7:0]连接端点 FIFO,其它配置引脚连接着 GPIF状态机的 RDY及 CTL引脚。为了确保各引脚的输入有充足的建立时间供 FPGA采样,FPGA的时钟输入应与 GPIF的内部时钟倒相。

本设计方案使用了一个控制端点(端点 0)和一个大端点(端点 2)传输数据。其中控制端点是所有 USB设备所必备的,它用于在设备枚举时传输 USB请求和相关数据,在本设计中,控制端点还用来传输专门设计的 USB厂商请求来控制配置进程、获取配置状态。大端点用来传输配置数据,由于配置数据需要及时、无误的传输,因此使用可以同时保证传输准确性和最大延时的中断传输方式,并设置端点缓存为 1KB、做 4倍缓冲,最大传输间隔为一个微帧(125us),且每个传输间隔内传输 3个有效载荷为 1KB的包(最后一个包的载荷可能小于 1KB),这样配置数据在 USB通道中的传输速率可达到 3*1KB*(1/125us) =24000KB/s。

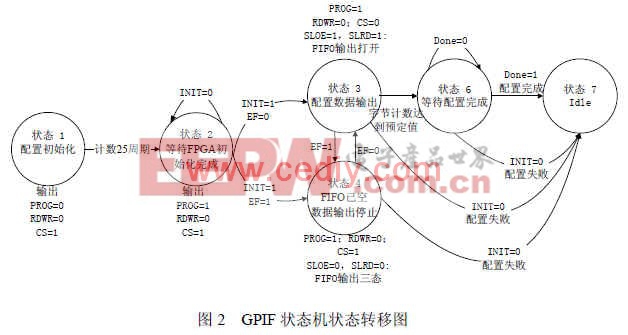

根据配置时序所设计的 GPIF状态机的状态转移图如图 2所示。配置时钟为 48MHz,所以 PROG低脉冲要维持 25个时钟周期,状态机会根据端点 FIFO的空满状态控制 FPGA的 CS引脚,确保 FPGA在 FIFO有配置数据输出的情况下进行数据采样,数据输出在字节计数达到 FPGA配置比特流文件的字节数值时停止,500万门的 XC3S5000为 13271936 bit[5]。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码