时钟分配芯片 在高速并行数据采集中的应用

多片ADC芯片并行采样的方式可以弥补单片ADC芯片采样率低的不足。通过对ADC芯片时钟的精确控制,可使采样系统在单位时间内获得更多的样本信息。理论上,如果单片ADC芯片的采样速率是f,那么通过M片ADC芯片的并行采样,可以实现M・f的采样率。多片ADC并行采样的结构框图如图4所示。

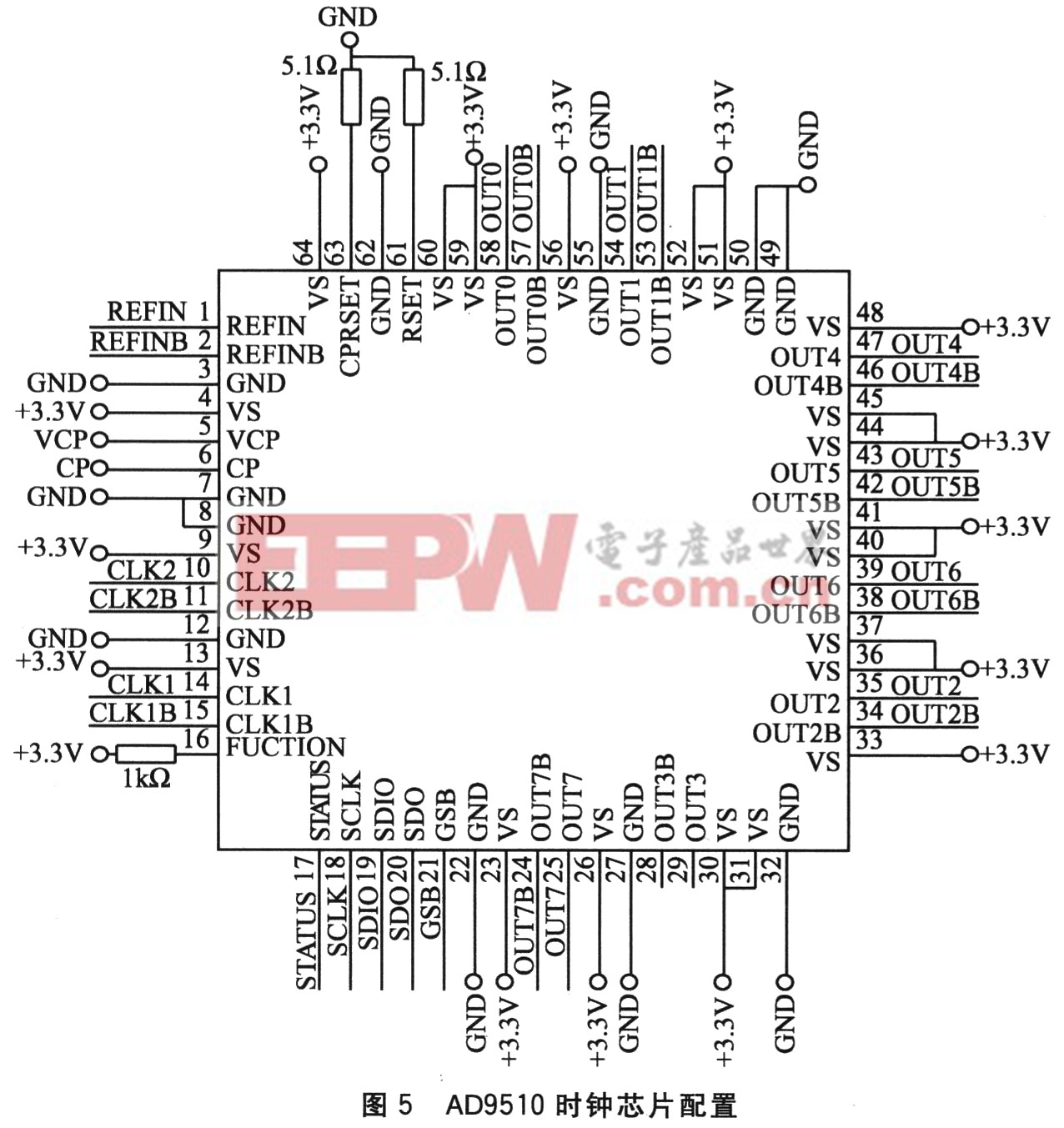

3 系统实现及时钟芯片配置

如上所述,利用M片ADC芯片理论上可以把采样率提高到单片ADC的M倍。那么利用4片采样率为250 Msps的ADC芯片AD9481,可以把采样率提高到1 Msps水平。其中时钟芯片的配置是设计的重要环节。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码