TIP41C低频大功率平面晶体管芯片设计

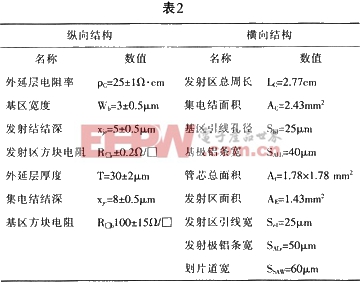

3 TIP41C晶体管的设计参数

TIP41C的纵向和横向结构参数如表2所列。该芯片的工艺流程如下:

N型外延片→一次氧化→一次光刻→干氧氧化→B离子注入→深基区扩散→二次光刻→磷预淀积→发射区扩散→特性光刻→特性hFE测试→P吸杂(PSG) →PLTO(低温氧化)→H2处理→三次光刻→QC检测(hFE、BVCBO、BVCEO)→蒸铝→四次光刻→铝合金→QC检测VBESAT→五次光刻 →PI胶钝化→中测抽检电参数→背面减薄(220μm)→蒸银→中测测试电参数→入库

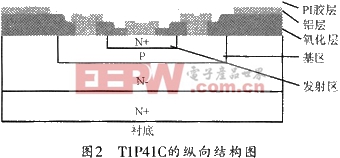

图2所示是TIP41C的纵向结构图。

由于作者所在单位的生产车间设计比较简单,车间环境净化程度不高,因此,在一次氧化、基区扩散工艺中采用TCA工艺来对一次氧化、二次氧化过程中Na +的污染进行有效控制,发射区扩散采用P-吸杂工艺来控制三次氧化过程中Na+的产生,表面钝化则采用PI胶工艺来保证外界环境不影响芯片表面,同时进一步吸收、稳定氧化层正电中心的移动,从而使芯片ICEO漏电大大减少,目前,TIP41C的电参数达到国际先进水平。

4 结束语

大量生产数据表明,我司设计的TIP41C晶体管芯片生产成本低,芯片尺寸1.78×1.78 mm2(为目前市场最小),生产原材料完全采用国产材料,目前,该芯片的关键电参数(大电流特性和饱和压降)已达到国际先进水平,因而具有极强的市场竞争力。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码