10~37 GHz CMOS四分频器的设计

1 引言

随着通信技术的迅猛发展,人们对通信系统中单元电路的研究也越来越多。而分频器广泛应用于光纤通信和射频通信系统中,因此,高速分频器的研究也日益受到关注。分频器按实现方式可分为模拟和数字两种。模拟分频器可由注入锁定等结构实现,一般具有工作频率高、功耗低等优点,但是分频范围较小,芯片面积较大。数字分频器基于触发器结构,一般分频范围较宽,芯片面积较小,但相对于模拟分频器其工作频率较低,功耗较大。这里采用UMC 0.13 um的CMOS工艺(其特征频率fT约100 GHz),在电源电压为1.2 V时,实现一个高速、宽分频范围的数字四分频器。

2 电路设计

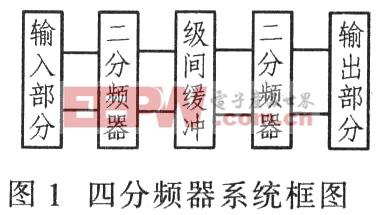

图1为四分频器的系统框图。它由两个二分频器级联而成。为了实现级间隔离和电平匹配,在两个二分频器之间加入级间缓冲电路。为便于区分这两个分频器,将前一个二分频器称为高速二分频器,后一个二分频器称为低速二分频器。因为要测试电路,需考虑输入和输出端口的阻抗匹配。为解决这些问题,电路中设计输人和输出部分。输入部分除实现输入阻抗匹配外,还要提供直流偏置。输出部分用以保证测试时的阻抗匹配以及得到一定的输出信号幅度。

2.1 二分频器

这里采用的二分频器为全差分的共栅动态负载结构,其框图和电路图如图2a和图2b所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码