一种自动变模控制的宽频带全数字锁相环

2 系统设计和计算机仿真结果

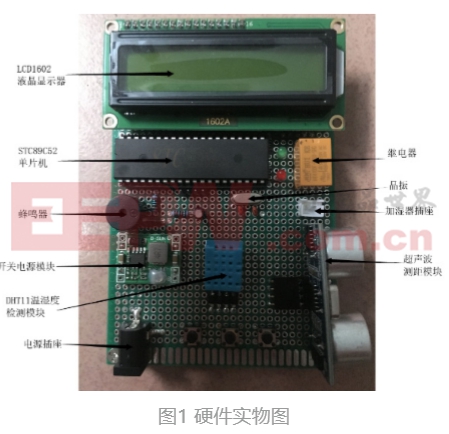

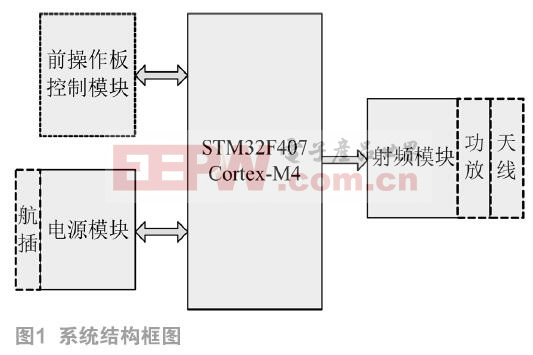

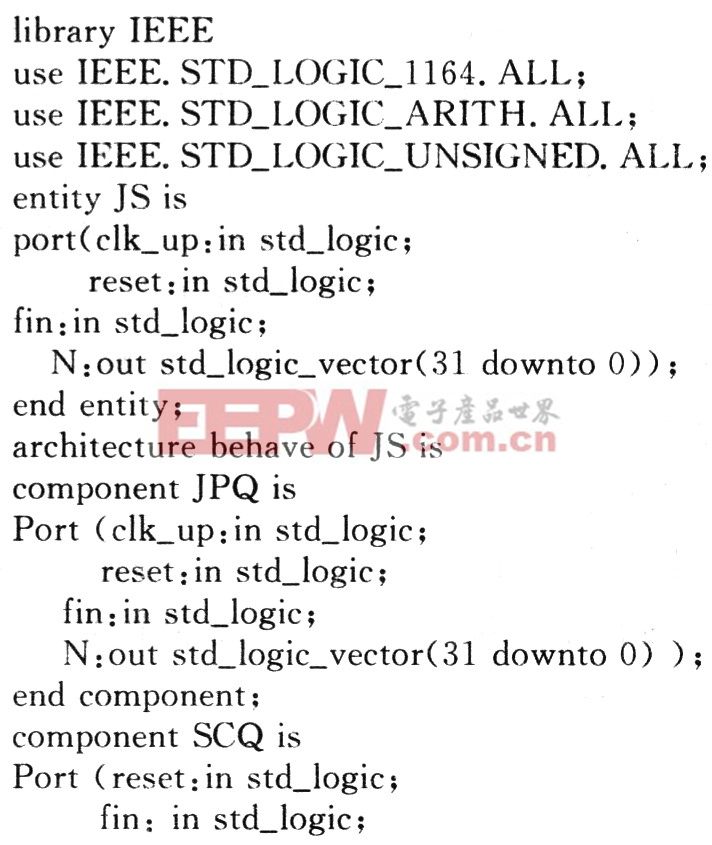

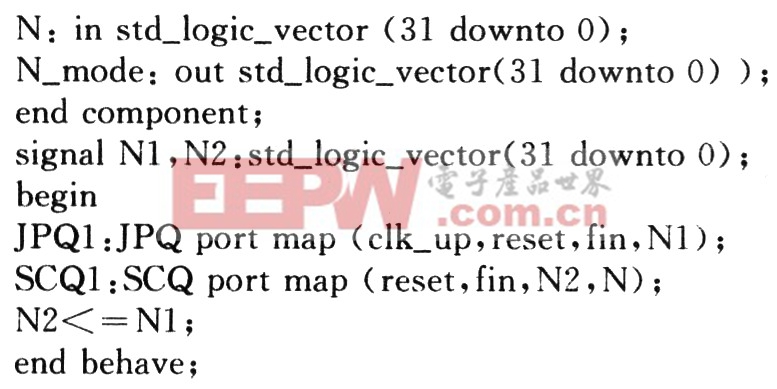

该设计在Altera公司生产的QuartusⅡ7.1开发软件平台上,运用自顶向下的系统设计方法,首先根据系统各功能模块的要求,使用VHDL语言编写程序,设计出环路各个部分的逻辑电路,并进行仿真验证。然后,再将各个部分组合起来进行系统设计和仿真。最后,用FP-GA芯片予以实现。限于篇幅,这里只对鉴频锁存模块的VHDL设计、仿真作为一个列子具体给出。其余模块不再赘述。该模块顶层部分的VHDL源代码如下:

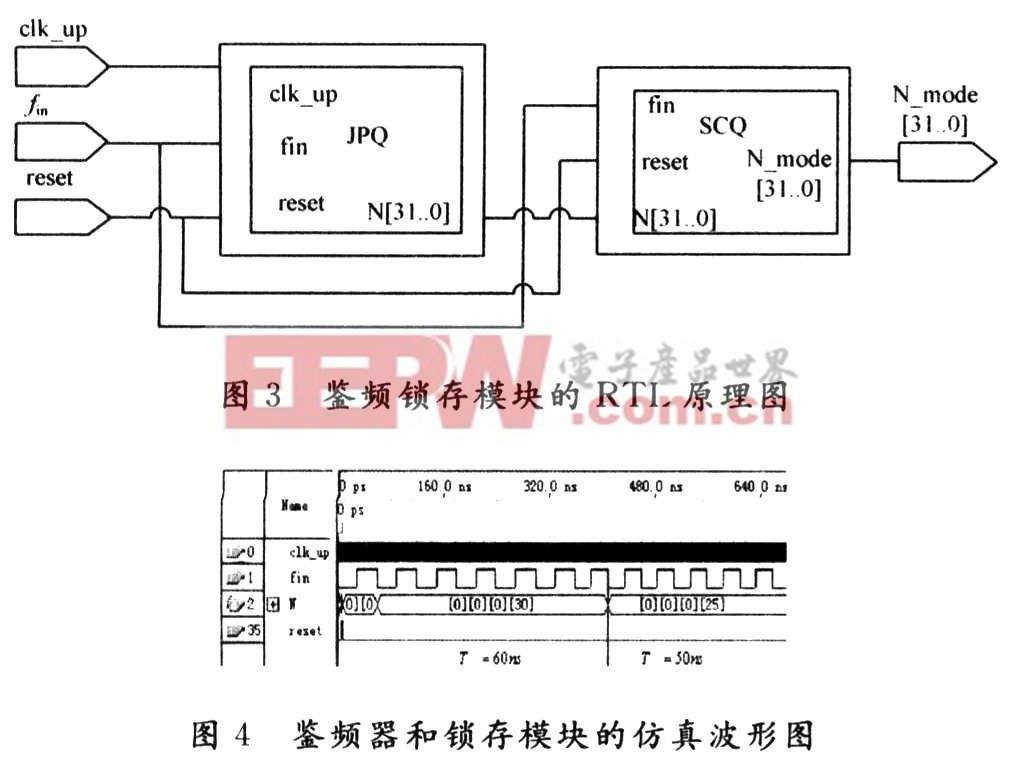

图3为QuartusⅡ7.1综合出的鉴频锁存模块的RTL原理图。图中JPQ,SCQ分别是由底层的VHDL代码综合出的鉴频器和锁存器,实现对输入信号鉴频和锁存的功能。图4为QuartusⅡ7.1的时序仿真波形图。图3中clk_up=1 ns为鉴频锁存模块的时钟源,fin为系统的输入信号ui的输入端,reset为系统的复位信号,N[31..0]为锁存器输出的鉴频结果。仿真结果表明该模块可以正确的完成鉴频和锁存的功能。

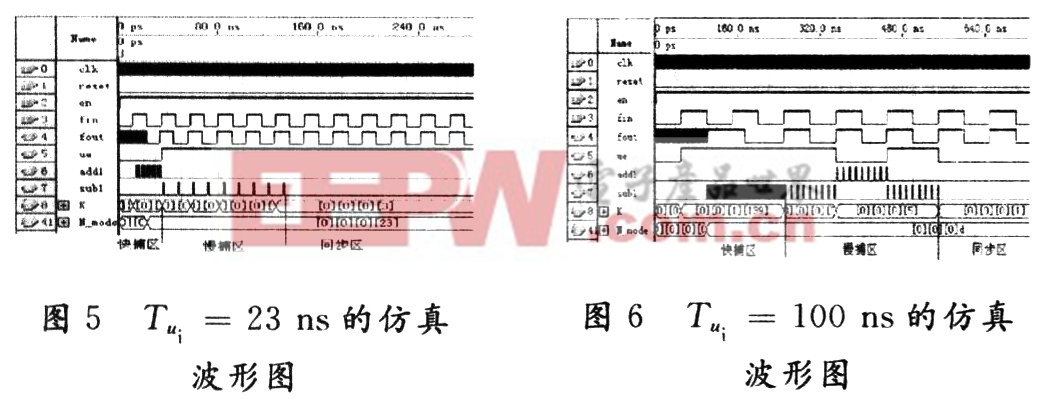

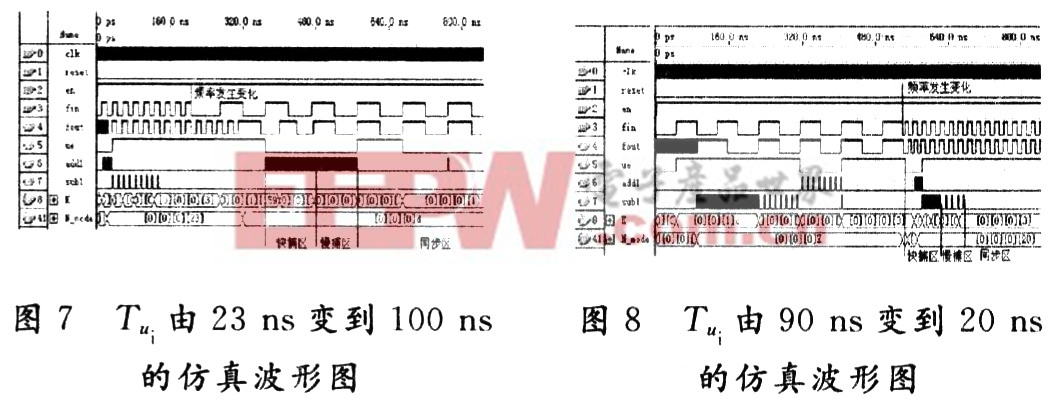

环路中各部分的设计仿真完成之后,再对整个系统进行设计和验证。在仿真图中clk为系统时钟;reset为复位信号;en为系统使能信号;fin和fout分别为输入输出信号;ue表明fin是超前还是滞后fout;add1,sub1是“加”、“扣”脉冲信号;K为fin和fout之间相位误差的量化值;N_mode为除N计数器的N值。自动变模控制电路根据输入与输出信号之间误差的大小,将环路的工作过程分为:快捕区、慢捕区和同步区。图5为输入信号周期Tui=23 ns的仿真波形图。图6为输入信号周期Tui=100 ns的仿真波形图。

图5和图6表明:该设计对输入的高频和低频信号都具有快的跟踪性能。图7为输入信号周期Tui由23 ns变到100 ns的仿真波形图。图8为输入信号的周期Tui由90 ns变到20 ns的仿真波形图。图7和图8表明:该设计对频率突变(高频突变到低频和低频突变到高频)的输入信号具有快的跟踪性能。

3 结 语

通过计算机仿真可以看出:设计的全数字锁相环具有很快的锁相速度,大量的实验表明在7个输入信号周期内环路就进入锁定状态。从图5和图6的仿真结果可以看出,设计的全数字锁相环锁频范围很宽。另外,锁相精度和系统的外部高频时钟有很大关系,如果时钟频率很高,那么锁相精度就越高。同时,外部高频时钟与该全数字锁相环的带宽也有很大的关系,在鉴频锁存模块是把外部高速时钟分频后的时钟作为时钟源的,因此,外部高频时钟频率越高,经过鉴频得到的分频值N才能越准确。总之,该设计的自动变模的全数字锁相环在外部时钟频率很高的情况下,不仅具有较快的锁相速度,而且具有较宽的锁频范围和较高的锁相精度。

该设计的全数字锁相环结构简单,易于集成,可采用VHDL语言完成系统设计,方便使用EDA软件进行综合仿真,可制成片内锁相环。下一步需要重点做的工作是:研究如何应用环形数控振荡器,使用控制字来控制环形数控振荡器的输出代替该设计中的外部高速时钟源;另一方面,在除N分频模块研究如何使用小数分频的技术提高了系统的精度。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码