基于DSP Builder的脑电信号小波处理

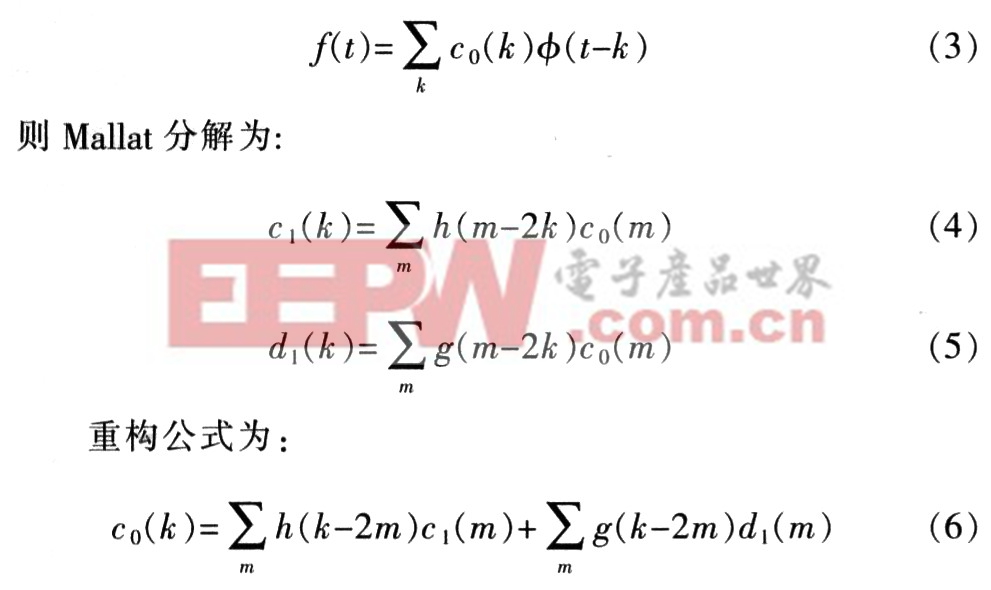

设信号为:

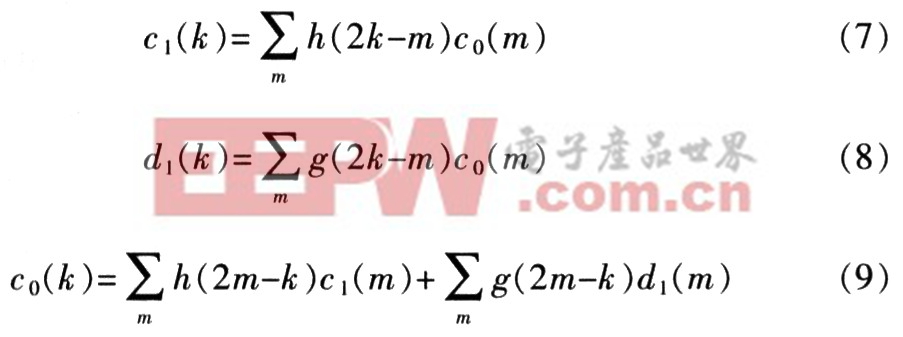

由于φ(-t)和φ(t-s)为构造正交小波的多分辨率分析尺度函数,因此上述分解和重构公式中取h(n)为h(-n)或h(n-s)均可。为了讨论方便,且不失一般性,可将上述分解公式和重构公式重写为:

带入式(9)得:

则c0(k)=c0(k-2N-1),式(13)得到的信号是式(12)得到信号的延迟。由于序列h(n)和g(n)为因果序列,所以式(13)对应的滤波器为因果滤波器。采用式(7)和式(8)继续分解信号低频分量或低频分量与高频分量.可得多级分解或小波包分解。

3 基于DSP Builder的小波变换设计实现

考虑到瞬态脉冲信号的短时性,选择具有紧支集的Daubenchies小波作为分析小波,这样有利于突出瞬态信号特征,DB小波函数具有良好的正交性和紧支撑性,可较好地表现频域信号的连续性和突变性,在实际工程应用中效果较好。故这里采用DB小波对脑电信号进行4级分解重构。滤除脑电信号中存在的直流成分或缓慢基线漂移。选取DB2小波,此时M=3,且低通滤波系数(尺度函数系数)如下:

由于浮点数在FPGA中实现比较复杂,为了减少FPGA的运算量和资源,可将滤波计算转换为整数运算和移位运算,为此首先需将以上滤波器系数转化为整数,对每个滤波器系数采用16位字长进行量化,即乘以215后取整数,而对滤波器的输出信号有移15位即得到实际输出。

以DSP Builder为平台,对式(7)、式(8)和式(13)算法进行系统级建模、仿真,再利用Signal Compiler生成HDL文件,然后利用Quartus II进行时序仿真验证。

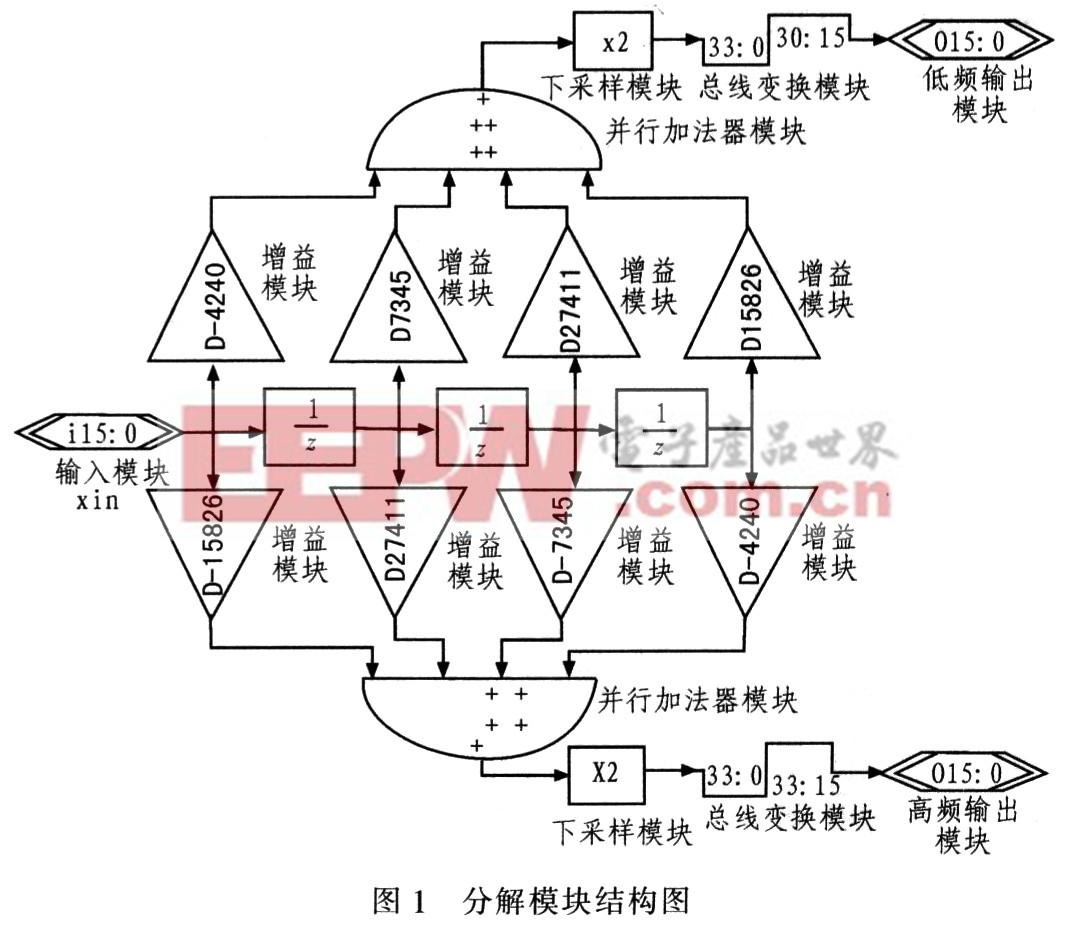

3.1 DSP Builder实现lD-DWT分解

分解模块的结构如图1所示。信号并行从4级延迟线输出,与FIR滤波器系数进行卷积,然后再偶抽取便可得到近似部分和细节部分的结果。二次抽取模块采用DSP Builder的下采样模块,利用Signal Compiler生成HDL文件。

为了减少系统耗用的硬件资源,舍去输出结果的低8位,保证分解前后信号保持同样能量级。从图1中可知,各个子模块并行工作,子模块之间无需任何交叉信号,数据从输入端以流水线的方式向后传递,实现实时流水线工作。二级分解模块的设计原理同一级分解模块。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码