基于DDS技术的杂散分析及抑制方法

3.3.1 PLL+DDS频率合成原理

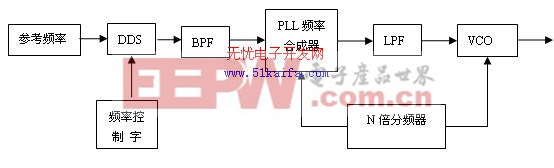

将DDS技术和PLL频率合成技术结合起来,用一个低频的DDS源激励一个PLL系统,用PLL环路将DDS信号倍频到高频信号,用滤波器滤除DDS输出信号杂波干扰,从而使系统同时具有锁相环技术和DDS技术的优点,使输出的信号满足电路的需要。系统组成如图2所示

图2

3.3.2 PLL+DDS频率合成器中的杂散抑制

当DDS源驱动PLL锁相环时,因为PLL锁相环相当于一个高Q值的跟踪滤波器,其带宽一般不大于100KHz,所以DDS中的大部分杂散会被抑制的很好,从而DDS输出信号中的杂散偏离主谱线距离大于锁相环路带宽的杂散不会恶化。在PLL+DDS系统中,应根据DDS的原理选择适当的时钟频率和输出信号频率,使DDS输出信号与边端的杂散处于相对理想状态,从而提高了系统的频谱纯度。

3.3.3 PLL+DDS频率合成器的实现

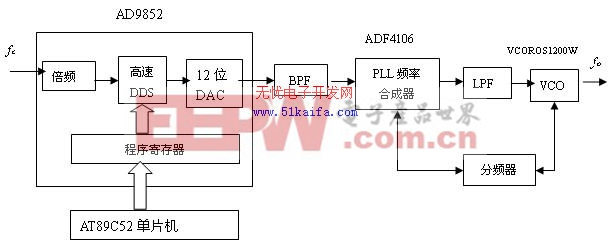

PLL+DDS频率合成器的组成如图3所示,下面介绍所选用的主要器件:

1. DDS部分

选用AD公司的AD9852高度集成化芯片,它采用了先进的DDS技术,结合内部高速、高性能D/A 转换器和比较器,形成可编程、可灵活使用的频率合成功能。当提供给AD9852精确的频率时钟源时,AD9852将产生高稳定、可编程频率相幅的正弦波。 AD9852使用先进的CMOS技术,使得提供给这个高性能芯片的工作电压仅为3.3V。

2. PLL合成器部分

PLL合成器部分采用AD公司的ADF4106,它主要由低噪声数字鉴相器、精确电荷泵、可编程分频器、可编程A、B计数器及双模牵制分频器等部件组成。数字鉴相器用来对R计数器和N计数器的输出相违进行比较,然后输出一个与二者相位误差成比例的误差电压。鉴相器内部还有一个可编程的延迟单元,用来控制翻转脉冲宽度,这个脉冲保证鉴相器传递函数没有死区,因此降低了相位噪声和引入的杂散。

图3

4 结束语

直接数字频率合成(DDS)是一种新型的频率合成技术,它代表了频率合成技术数字化发展的新方向。但是,DDS所固有的杂散和噪声,并且在频率升高时杂散和噪声也随之增加,使它的应用范围有一定的限制。所以如何减少DDS输出中的杂散和噪声成分是当今DDS研究中的核心问题之一。本文所介绍的抖动注入技、平衡DAC结构以及关于ROM幅度表压缩的几种算法,都能有效地减少DDS输出信号中的杂散。尤其当要求得到既有高的频率分辨率,又有较快的转换速度和较低噪声的高频甚至微波信号时,DDS+PLL技术就显现出了较强的优越性,经过实际的工程应用,达到了令人满意的效果。总之,随着现代科技的不断发展 DDS的性能会不断地完善,DDS应用领域也会不断地拓展。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码