基于Actel FPGA的I2C IP的应用

(3)Core I2C内部寄存器

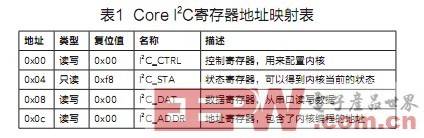

Core I2C的寄存器的地址映射如表 1所示。

● 控制寄存器——I2C_CTRL

Bit7:串行时钟位2,和第0位、第1位一起决定分频系数。

Bit6:I2C使能位,1表示I2C被使能,否则被禁止。

Bit5:起始标志位,1表示起始标志位有效,总线在空闲时将会产生一个起始状态位。

Bit4:停止标志位,1表示停止标志位有效,总线将会产生一个停止状态位。

Bit3:串行中断标志位,在状态寄存器的值被更新以后,这位必须被清零。

Bit2:主/从机设置位,1表示工作在从机模式,0表示工作在主机模式。

Bit1:串行时钟位1,和第7位、第0位一起决定分频系数。

Bit0:串行时钟位0,和第7位、第一位一起决定分频系数。

Core I2C时钟频率的定义如表 2所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码