关于C64x+ DSP高速缓存一致性分析与维护

高速缓存一致性问题分析

在任何时刻,内核或者其它主机访问存储器中数据时,由于CACHE的存在造成不能够得到最近更新过的数据,就会出现CACHE一致性问题。CACHE的一致性问题分为两个大类:内核读一致性问题和内核写一致性问题。在下面两个小节中,分别描述了这两种情况的模型:

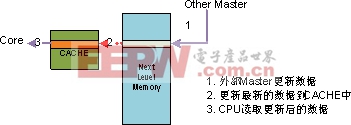

内核读一致性模型

图 3给出了内核读一致性的模型。在这个模型中,CACHE一致性问题的存在取决于图中虚线箭头指示的第二步操作能否在内核从CACHE中重新读数据之前完成。如果不能,则会造成内核读取的数据不是其它主机更新后的数据,而是原来CACHE中的内容,从而导致一致性的问题。

图 3 内核读一致性模型

L1P CACHE对L2内存或者DDR2外存中的代码进行缓存。当内核第一次对L2或者DDR2中的代码进行读操作的时候,由于代码不在L1P CACHE中,CAHCE硬件会将L2或者DDR2中的代码读到L1P CACHE中。内核可以得到最新的代码,不存在一致性的问题。此后,如果其它主机更新L2或者DDR2中的代码,然后内核再次读取此部分代码时,会发现相应的代码已经存在L1P CACHE中,此时内核会直接从L1P CACHE中读取代码。由于内核不能得到最新的代码,就出现了内核读一致性的问题。L1D 内核读一致性问题的原理和L1P相同,只是L1D缓存的是L2或者DDR2中的数据。

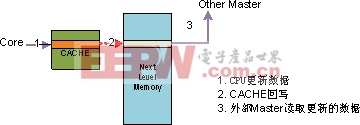

内核写一致性模型

图 4给出了内核写一致性的模型。在这个模型中,CACHE一致性问题的存在取决于图中虚线箭头指示的第二步操作能否在其它主机从存储器中读数据之前完成。如果不能,会造成其它主机从存储器中读到的数据是原来的数据而不是内核更新过的数据,从而导致一致性的问题。

图 4 内核写一致性模型

当内核对L2或者DDR2中的代码/数据进行写操作的时候,如果代码/数据已经在L1 CACHE中,新的代码/数据会被更新到L1 CACHE中。当其它主机从L2或者DDR2中读代码/数据的时候,会直接从L2或者DDR2中读取相应的内容,如果L1 CACHE中新的代码/数据未被更新到L2或者DDR2中,则其它主机读取的不是更新后的内容,就会出现内核写一致性的问题。

C64x+ 一致性分析

C64x+上的CACHE一致性问题,需要根据放置代码/数据的相应位置进行分析。由于在C64x+平台上,L1P、L1D和L2内存既可以作为CACHE又可以作为存储器使用,因此,在分析一致性问题的时候,需要考虑以下几种情况:

1) 代码在L1P存储器中;2) 代码在L2存储器中;3)代码在DDR2存储器中;4)数据在L1D存储器中;5)数据在L2存储器中;6)数据在DDR2存储器中。

对于1),由于代码直接在L1P存储器中,不需要进行CACHE,所以不会存在一致性的问题。

对于2)和3),涉及到L1P CACHE,存在代码的更新能否被内核读到的问题。代码的更新分成两种情况:一是内核在运行过程中对代码进行修改;二是其它主机对代码的修改。这两种情况下,都会存在CACHE读一致性问题,需要由软件来维护。

对于4),数据直接在L1D存储器中, 内核始终能够读到其它主机更新到L1D内存中的内容,内核写过的数据也能够被其它主机直接从L1D内存中读到。所以不会存在一致性的问题。

对于5),数据在L2存储器,按照上面的分析,会存在CACHE读和写一致性的问题。在C64x+平台上这种情况下的一致性问题会由硬件自动维护。

对于6),也会存在CACHE读和写一致性的问题,这种情况需要软件进行CACHE一致性的维护。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码