基于FPGA的高阶QAM调制器的实现

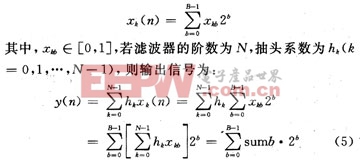

本设计采用分布式算法(DA)原理,利用FPGA查找表代替乘法器来实现FIR滤波器,其基本思想如下:

假设输入信号数据位为B位,则滤波器在n时刻的第k个输入为:

从式(5)可以看出,FIR滤波器中乘加单元的运算是算法核心。如果建立一个查找表(Look Up Table,LUT),表中数据由所有固定系数(h0,h1,…,hN-1)的所有加的组合构成(和用sumb表示,6∈[0,B-1]),那么,用N位输入数据构成的N位地址去寻址LUT,如果N位都为1,则LUT的输出是N位系数的和,如果N位中有0,则其对应的系数将从和中去掉。这样乘加运算就变成了查表操作。整数乘以2b可以通过左移6位实现。

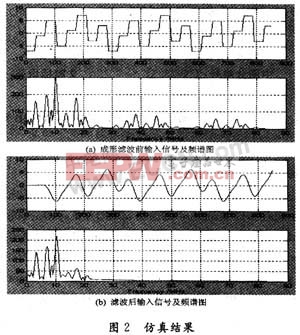

对于本系统,码元速率为25.92 Mbaud,滚降系数选取为0.5,抽头个数取N=16,抽头系数精度取10 b,输入数据为4 b,输出精度取9 b。仿真结果如图2所示。

从图2可以看出:码元速率为25.92 Mbaud的基带信号经成形滤波后,频谱被限制在20 MHz范围内。

3.2 正交调制器的设计

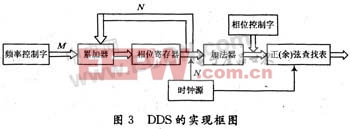

经成形滤波后的两路基带信号分别对DDS(DirectDigital Synthesizer)产生的两路正交的载波进行调制,然后进行矢量相加形成调制信号输出。DDS的FPGA实现框图如图3所示。

DDS的基本原理是利用采样定理,利用查找表法产生波形。相位累加器是DDS系统的核心部分,每来一个时钟脉冲,累加器将频率控制字M与相位寄存器输出的累加相位数据相加,把相加后的结果送至相位寄存器的数据输入端;相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端,以使累加器在下一个时钟的作用下继续与频率控制数据相加。这样,相位累加器在参考时钟的作用下,进行线性相位累加,当累加器累加满量时就会产生一次溢出,完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,累加器的溢出频率就是DDS输出的信号频率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码