基于NiosII的IP Camera传输系统实现

1 引言

随着网络技术的发展,人们对监控功能要求越来越高,网络摄像头以其特有的优势改变了传统监控手段,为远程实时监控提供了出色的解决方案。人们只需打开网页或视频浏览器就可实时查看需要监控场所的安全情况。

2 系统的硬件设计

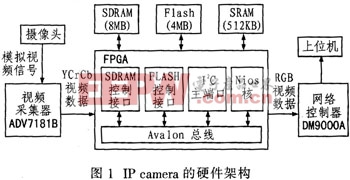

IP Camera的硬件架构如图1所示,这是笔者参与开发的一种基于Altera公司NiosII嵌入式软核CPU的网络视频传输设计方案,实现了以太网内视频数据传输。FPGA采用的是Altera公司的Cy-cloneII系列的EP2C35F672C6器件。IP camera主要是由视频采集、Cyclone FPGA及系统存储和网络传输等3部分组成。由于Cyclone FPGA及系统存储的电路设计具有一定的通用性,所以这里仅介绍视频采集和网络传输的电路设计。

2.1视频采集模块设计

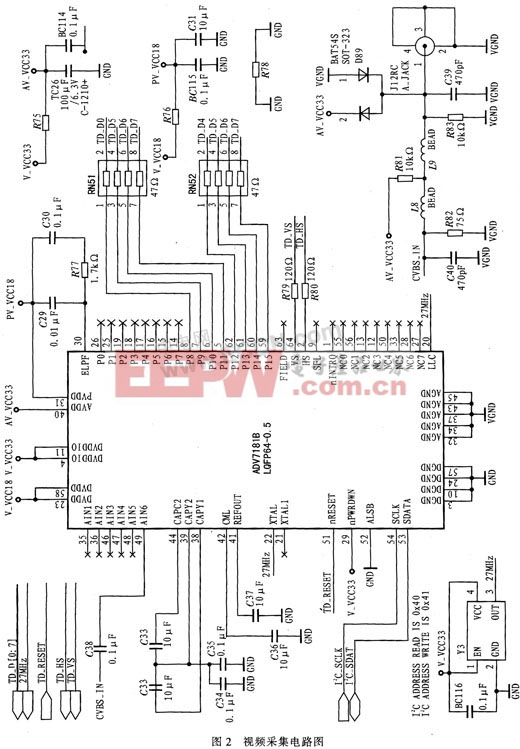

本系统设计的视频采集器件采用ADV7181B。ADV7181B是一款集成的视频解码器,通过配置可以接收CVBS复合视频、S-Video及YPrPb分量多种模拟信号,ADV7181B的数字输出是16位或8位、并与CCIR656标准兼容的YCrCb4:2:2视频数据,还包括垂直同步VS、水平同步HS及场同步信号。

本系统设计选用ADV7181B的AIN6作为CVBS复合视频信号的输入,ADV7181B的输出数据采用8位的数据宽度。ADV7181B的27 MHz时钟由FPGA提供,FPGA通过I2C总线读/写ADV7181B的寄存器控制ADV7181B,ADV7181B的I2C总线读地址为0x40,写地址为0x41。ADV7181B的8位YCrCb4:2:2视频输出数据及其他输出信号直接连接至FPGA。视频采集电路模块电路图如图2所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码