基于FPGA的多通道校准算法同步实现

表1为多通道校准算法的FPGA资源占用列表,从系统资源占用情况可以看出:多通道校准算法FPGA实现过程中,如果再加上前后端处理程序一起编译,则输入输出端口将减少,资源占用也将减少,并不影响系统实现。其它各种资源占用量都较少,完全符合FPGA设计要求。

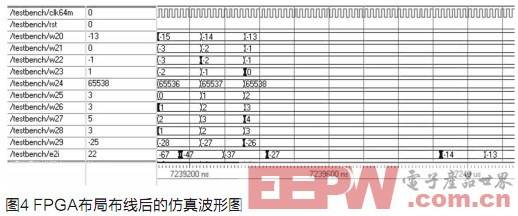

FPGA布局布线后的仿真波形如图4、图5所示。

从仿真结果(图4,图5)和ISE 8.2i的综合报告可知,该校正模块的最高时钟频率达到102.5MHz。

最后,由MATLAB仿真和FPGA布局布线后仿真得到的权值,经过MATLAB仿真形成新的方向图,如图6所示,可以看出,两种方向图基本一致。因此,基于FPGA的多通道校准同步算法的实现完全符合系统要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码