AD7656-1菊花链的多通道数据采集接口设计

2.2 AD7656-1菊花链的配置

AD7656-1要工作在菊花链方式,其数据输出必须设置为串口模式,且在串口模式下,AD7656-1必须配置成硬件模式。所谓的硬件模式是通过对器件引脚的固定连接,确定AD7656-1 芯片唯一的工作方式,此时AD7656-1也不能配置成软件工作模式了。AD7656-1菊花链配置的主要原则如下:

①在多片级联的AD76561中,位于级联最远端的芯片不能配置为菊花链工作模式,即其DCEN引脚置低电平(数字地);但其下流数据链的每片AD7656-1必须配置为菊花链工作模式,即DCEN引脚都要置逻辑高电平(VDRIVE)。

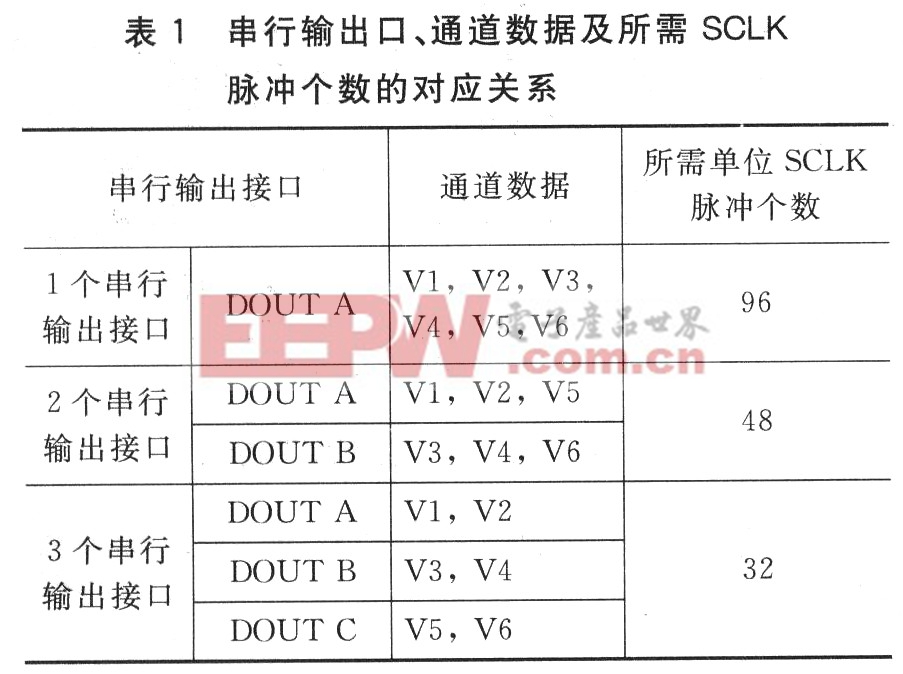

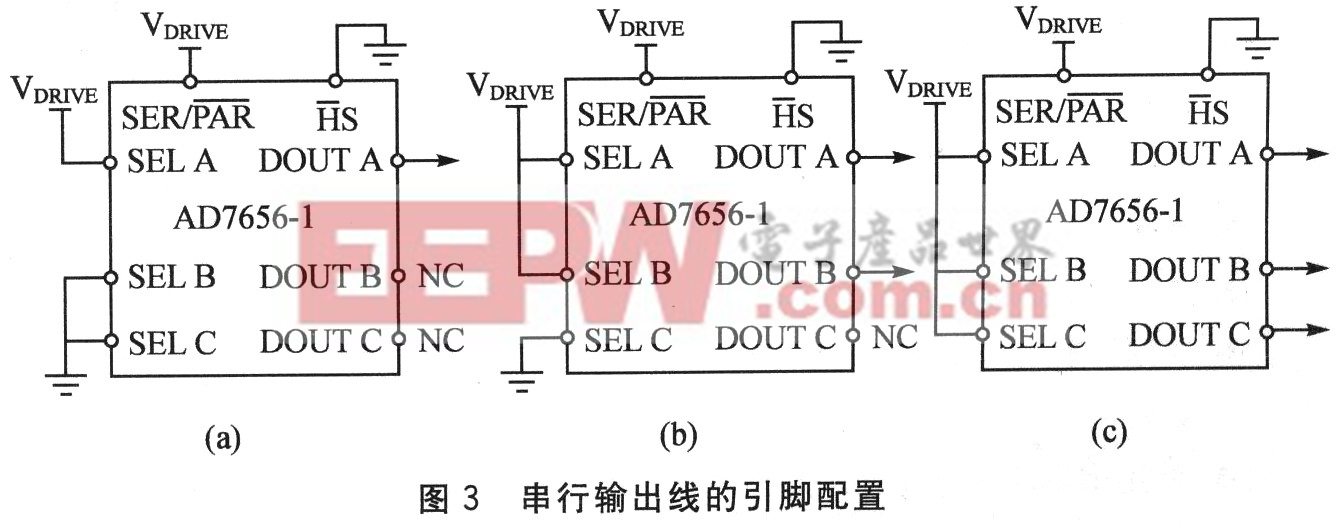

②SEL A、SEL B、SEL C对应使能DOUT A、DOUT B、DOUT C串口输出口。要选用DOUT X串行输出口,就置对应的SEL X为逻辑高电平,其余不用的SEL引脚必须置逻辑低电平。图3(a)、(b)、(c)为1~3个串行输出口的引脚配置。(图中“NC”表示未连接)

③菊花链中的每片AD7656-1的串行数据输入/输出(DCIN X/DOUT X)必须遵循同一配置,即有几个DCIN输入就有几个DOUT输出。

④菊花链中的每块AD7656-1的CONVST X(X=A、B、C)都要接主控处理器发送来的CONVERT信号,即配置为每块AD7656-1的V1~V6通道同时采样。

3 AD7656-1菊花链与S3C2410A接口设计

3.1 硬件电路设计

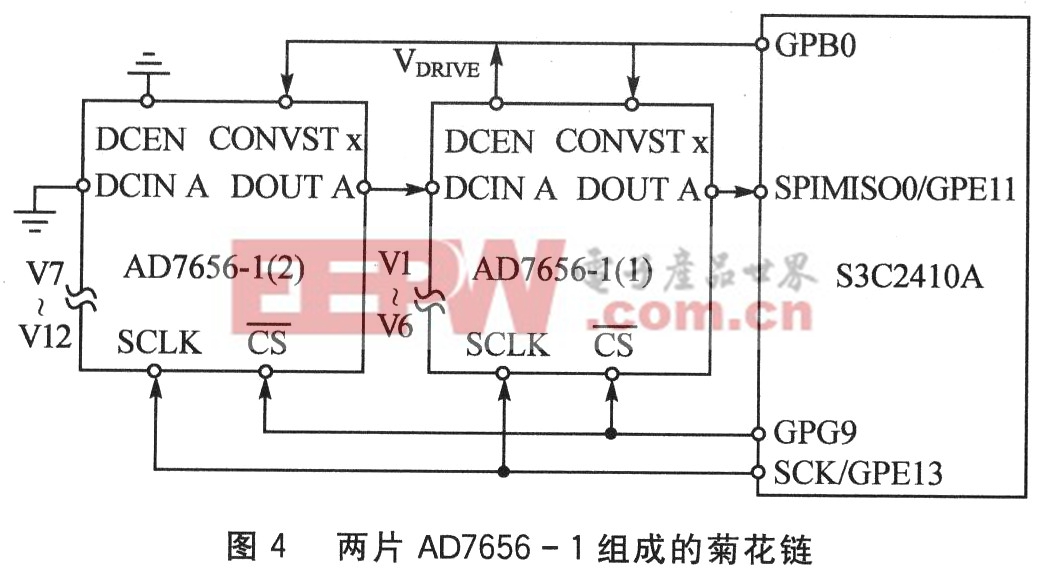

采用2片 AD7656-1配置成菊花链,可实现12通道同时采样,数据通过DOUT A口输出,S3C2410A用同步串行接口0(SPIO)接收数据,如图4所示。S3C2410A的GPEll引脚实现片上同步串行接口SPlO的 MISO功能,GPEl3(SCK)引脚实现SPIO接口的同步时钟输出,GPFO引脚配置为中断EINTO输入并与AD7656-1(1)的BUSY脚相连;GPBO设置为PWM输出,GPG9引脚没置为通用输出口,分别作为AD7656-1(1)和AD7656-1(2)的CONVST和CS的控制信号输入。AD7656-1连接外围电路时,必须对关键引脚进行必要的设置:AD7656-1(1)、AD7656-l(2)的DVCC、AVCC、 VDRIVE、REFIN/OUT和VSS引脚须并联一个1 μF的去耦电容;为了与S3C2410A的3.3 V的接口匹配,VDRIVE接+3 V电源;STBY接VDRIVE,选择正常模式;RANGE接地表示选择输入范围±10V;H/s接数字地选择为硬件配置;SER/PAR接 VDRIVE,RD接数字地,选择为串行模式。AD7656-1(1)的DCEN接VDRIVE,配置为菊花链模式,且SEL A接VDRIVE,SEL B、C,DCIN A、B、C接数字地;AD7656-1(2)的DCEN接数字地,配置为非菊花链模式,且SEL A接VDRIVE,SEL B、C,DCIN B、C接数字地。具体配置如图5所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码