超高频段RFID标签的数字电路设计

4.2 译码模块具体实现方法

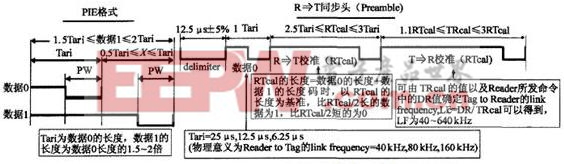

读写器发出的命令采用PIE (pulse.interval encoding)格式,命令以同步头(preamble)开始,如图3所示。译码模块的实现方法为:首先判断同步头,标签对输入信号进行检测,一旦检测到下降沿说明可能是一条新命令的定界符(delimiter),马上计数低电平,将计数值存人寄存器count0中,同时检测输入信号是否有上升沿跳变,若发现上升沿跳变,则数据清零重新计数,并把delimiter之后的计数值存入寄存器count中,不断比较寄存器count0和count的值,依据图3所示的关系依次判断出delimiter, 数据0,RTcal(reader to tag calibration),TRcal (tag to reader calibration), 确认同步头;然后把同步头之后的数据比RTcal/2短的作为数据0,比RTtcal/2长的作为数据1,从一系列高低电平中恢复出真正的1信号和0信号,依次存入命令寄存器,并提供控制状态机及校验模块的相关标志位。

图3 PIE格式,R=>T(reader to rag)同步

4.3 CRC校验和产生模块

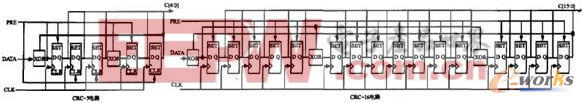

UHF RFID系统采用循环冗余校验(CRC校验)来判断数据的有效性和完整性,CRC校验可以保护读写器发出的RjT (reader to tag)命令和标签反向散射的TjR (tag to reader)序列。从数学角度来看,CRC校验是用将被处理的数据字节当作一个二进制多项式A ( )的系数,该系数除以发送方和接收方预先约定好的生成多项式g ( )后,将求得的余数P ( )作为CRC校验码。CRC的计算包括了要计算其CRC值的数据字节以及所有前面的数据字节的CRC值。当一个数据块被传输时,数据发送方计算此数据块的CRC校验码,并将此校验码附在数据块后一起传输。数据接收方计算所有接收数据的CRC值,其结果总是零,否则在传输过程中一定出现了传输错误。用零校验可以很容易地分析数据的完整性,避免代价很高的校验和比较过程。协议中采用线性反馈移位寄存器来实现CRC校验,CRC.5校验和CRC.16校验的电路示意图如图4所示。

图4 CRC-5和CRC-16电路

4.4 射频标签中的状态机

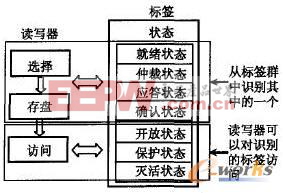

RFID标签所有的操作都基于由一系列逻辑控制的状态转换进行的,此为标签数字电路的核心部分。本设计采用有限状态机来实现此模块,这里用到了3类基本操作和7种典型的状态。如图5所示,当收到不同命令时,标签将会在7种状态间进行转换。选择(select)命令和盘存(inventory)命令用于从标签群中识别出特定的一个,标签所处的相应状态为ready,arbitrate,reply,acknowledged;一旦标签被识别,读写器即可发出访问(access)命令,读取标签的信息或将信息发送给标签,标签所处的相应状态为open,secured,killed。

图5 读写器对标签操作及标签的状态

识别多个标签时采用随机分槽防碰撞算法(slotted random anti.collision algorithm)解决冲突问题。读写器向读写范围内的每个标签发送包含参数Q (取值0 15)的Query命令,控制标签往各自的分槽计数器内载入一个由Q值决定的随机数(取值范围0~2Q.1),随机数的产生主要基于线性移位反馈寄存器 。读写器再发出其他inventory命令改变随机数的值,只有当随机数的值为0时,标签才会应答。若多个标签的计数器值同时为0时,这些标签同时应答,从而造成冲突。读写器检测到冲突后,发出inventory命令让冲突标签的随机数值从0000h(十六进制数)变到7FFFh,再通过设置新的Q参数来随机散列分槽计数器值,使得发生冲突的多个标签逐一被识别,保留一个处于活动状态的标签与读写器建立无碰撞通信,这样就有效地解决了冲突问题。虽然此种方法的判别线性度比二进制数搜索法低,但读取速度高,演算机制完整,可防范多种信号碰撞的可能性,大幅降低信号碰撞的几率。

4.5 编码模块

标签反向散射给读写器的数据采用FM0编码,图6给出了FM0编码的格式。

图6 FM0编码格式

FM0编码的数据前应以前同步码开始,选择哪种前同步码由读写器所发命令中的TRext参数决定;FM0编码在每个数据边界处倒转相位,并在数据0中间倒转相位。FM0编码具有记忆功能,一序列的信号中,后一位电平必须承接上一位末尾电平,所以需要一个寄存器存放上一位末尾处的电平信号,由此来判断下一信号的起始电平。根据读器所发命令确定标签返回数据的链路频率(LF:link frequency), 由内部时钟计数产生所需频率,以此作为标签返回数据的发送频率。为降低功耗,可以将全局时钟分频,降低时钟频率。为了准确实现编码的功能,需要在充分理解标准的基础上,严格定义该模块与状态机之间的接口时序。编码模块只有与状态机模块在时序上密切配合,双方才能正确地发送和接收信号。实现过程为:当状态机发送的使能信号有效时,编码模块进入编码状态,同时,状态机送出数据信号;编码模块被触发启动后,首先按照协议要求产生前同步码,再把要输出的数据依次编码,产生1 bit中高低各半的0信号或统一电平的1信号,串行送出;当状态机发送最后一位数据的同时,通知编码模块,状态机的数据已经发送完毕。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码