基于Xtensa的ASIP开发流程研究

前言

随着半导体工艺技术向着纳米尺度的发展,微电子技术进入SoC(系统芯片)时代,且沿着可靠性强、体积小、功耗低等方向继续发展。在下一代SoC设计流程中,系统级EDA工具的地位变得比以往更加重要,ESL(Electronic System Level)设计方法学将是设计下一代SoC的关键,因为逐渐缩短的上市时间需要硬件-软件并行设计。

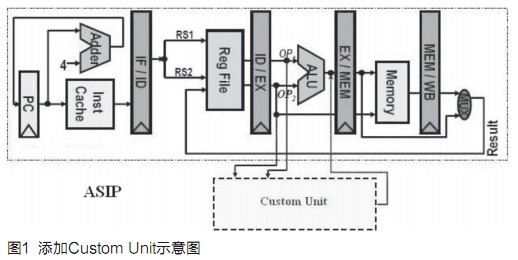

本文以Tensilica Xtensa可配置、可扩展处理器为开发平台,探索了高性能低功耗ASIP(Application Specific Instruction-set Processor专用指令处理器)开发流程。

ASIP设计理论

面向特定应用的ASIP处理器,既有ASIC执行特定应用的高效性,又有GPP处理器可编程的灵活性,能够简化设计复杂度、缩短设计周期、加快上市步伐,在SoC设计中得到了广泛的应用。如何快速高效地定制ASIP,使其满足运算性能、芯片面积、上市时间和功耗等要求,是一个极具挑战性的问题。设计者需要在ASIP指令集设计过程中在广泛的设计空间进行指令集探索,寻找满足设计约束的处理器体系结构[1-8]。因此迫切需要可以支持快速ASIP设计的行为级设计方法和合适的EDA工具。

关键词: RISC 编译器 ASIP Xtensa 体系结构 自定义指令 Xplorer XPRES XEnergy 200906

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码