基于Verilog的FPGA与USB 2.0高速接口设计

2.2 FPGA控制程序设计

CY7C68013A提供的端口FIFO的读写操作,与普通FIFO读写操作方式一样。CY7C68013A为每个端口提供了“空”标志、“满”标志和“ 可编程级”标志。FPGA检测这些信号,用于控制读写的过程。FPGA在完成这些端口FIFO的操作时,采用Verilog HDL硬件描述语言实现了FIFO的读写时序,并在ALTERA公司提供的QuartusⅡ8.O开发工具中综合编译并映射到FPGA中运行。

2.2.1 从属FIFO异步“读”操作

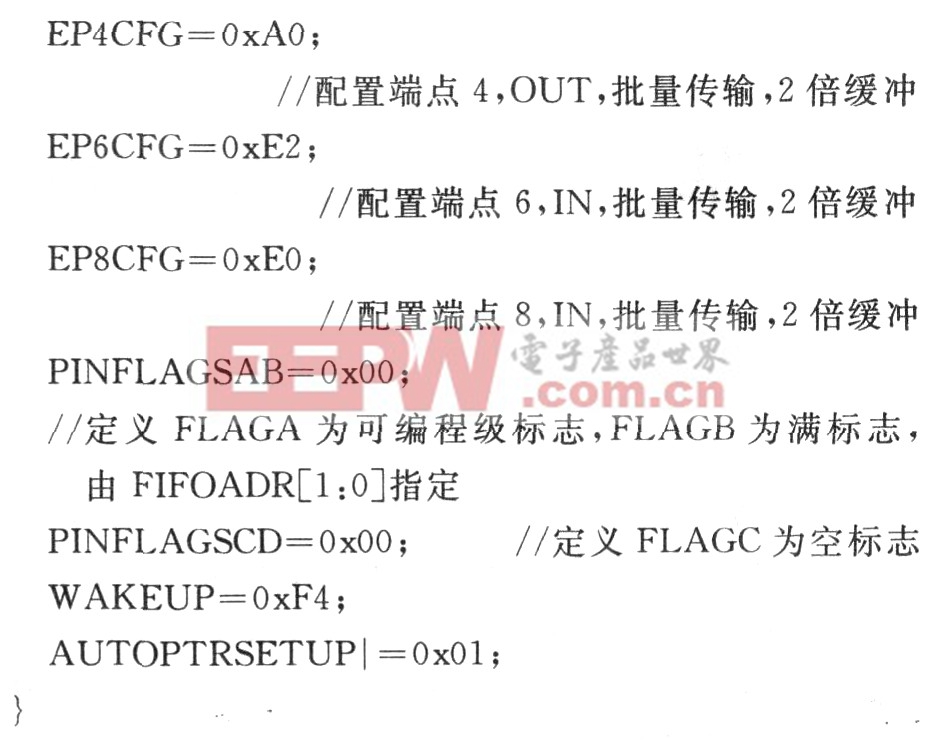

实现异步从属FIFO“读”的状态机如图3所示。其状态转移进程如下:

IDLE:当“写”事件发生时,转到状态1。

状态1:指向OUT FIFO,激活FIFOADR[1:O],转向状态2。

状态2:激活SLOE,如果FIFO空标志为“假”(FIFO不空),则转向状态3;否则停留在状态2。

状态3:激活SLOE,SLRD,传送总线采样数据;撤销激活SLRD(指针加1)和SLOE,转向状态4。

状态4:如果有更多的数据要求,则转向状态2;否则转向IDLE。

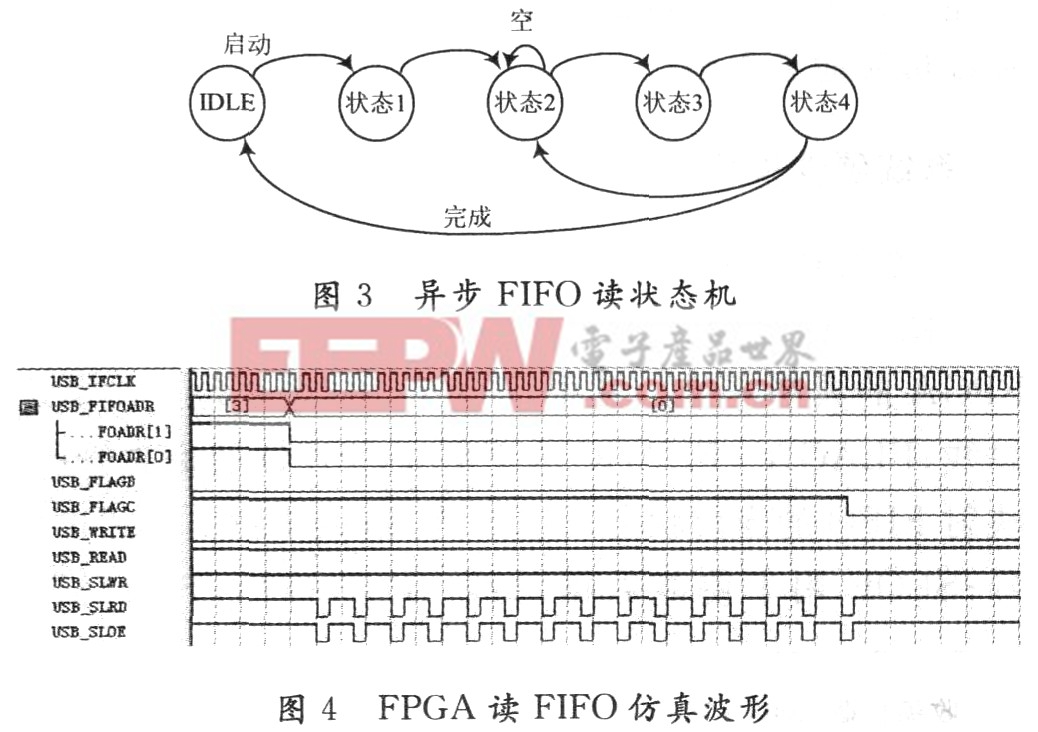

实现以上状态机的仿真波形如图4所示。

2.2.2 从属FIFO异步“写”操作

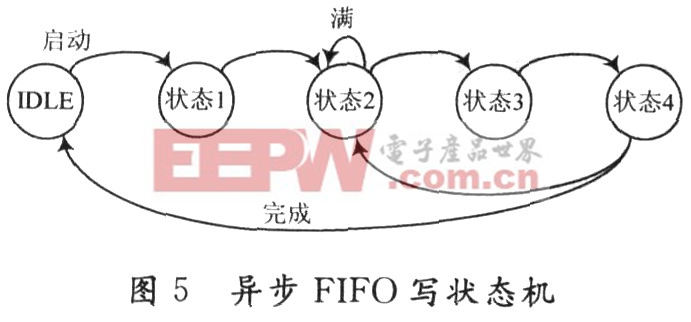

实现异步从属FIFO“写”的状态机如图5所示。其状态转移进程如下:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码