双口RAM在组合导航系统中的应用

1.3 令牌判优方式

令牌判优方式是一种快速数据交换方式。在此方式中有信令锁存逻辑,CY7C028内部提供了八个相互独立的锁存逻辑单元,最多可将RAM空间分成八个区段。这些锁存逻辑单元独立于双口RAM存储区,并不能控制RAM区、封锁两端CPU的读/写操作,而是被作为信令,只提供指示逻辑,由两端CPU按约定的规则,轮流地占用它们划定的RAM区,各区的大小及地址由软件自由设定,且左右端操作完全一样,只要不超过令牌的限制次数即可。当左右端口同时申请同一令牌时,令牌逻辑将裁定谁先占用,从而保证只有一个端口获取令牌。而在占用令牌期间,CPU可以按最高速无等待存取数据,这对实现高速、多CPU数据采集与处理系统无疑是非常有利的。但是,为了避免令牌方式争用出错,应尽可能使两端CPU分时占用同一RAM区。

2 双口RAM在组合导航系统中的应用

2.1 系统总体设计

导航系统的主要任务是测量飞行载体的即时位置、速度、航向等导航参数,具有实时性高、运算量大等特点。因此在导航系统中,计算机设计是系统设计的关键之一。在INS/GPS组合导航系统中,导航计算机的任务主要有三类[6]:

(1) 数据采集,包括采集惯性测量单元元件输出信号,接收外部系统校正信息,如GPS输出信息、初始位置信息等。

(2) 数据处理与运算,包括惯性测量元件的误差补偿、初始对准、导航参数解算、组合导航算法实现等。

(3) 输出导航数据及系统状态量,包括输出导航参数以及与其它设备交换信息等。

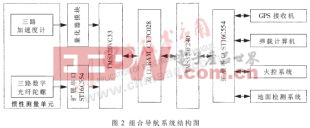

所有这些任务,如果都由一个CPU来完成,那么CPU在进行运算的同时,还要兼顾系统控制和数据输入输出,并响应频繁的中断,必然降低系统运行效率。所以,为了兼顾系统运行效率,减轻导航计算机负担,设计一种以TMS320VC33为主机和以TMS320F240为接口机的双DSP主从式系统。系统总体结构如图2所示。

主机TMS320VC33主要用来定时采样陀螺、加速度计的数据,并完成姿态阵计算、组合系统卡尔曼滤波器计算等导航解算。接口机TMS320F240主要完成系统相关状态的检测/控制,与GPS接收机、弹载计算机及其它外设的通信等任务。主机和接口机之间的通信利用双口RAM CY7C028实现。量化器模块主要是将加速度计输出的电流信号转换成主机可直接读取的数字量。此外,由于TMS320VC33和TMS320F240的串口资源有限,无法满足系统需要,系统中采用EXAR公司的ST16C554进行相应的串口扩展。

2.2 DSP与双口RAM的接口设计

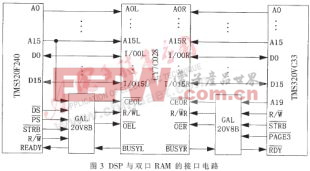

在组合导航系统中,CY7C028与两个DSP芯片TMS320VC33和TMS320F240之间的接口电路如图3所示[2~4]。TMS320VC33的数据线宽度为32位,而CY7C028的数据位宽为16位,因此采用将TMS320VC33数据总线的低16位与双口RAM的数据总线相连。TMS320VC33在发送32位的数据至双口RAM时,分两次完成,先写低16位,再写高16位。从双口RAM读取数据操作与发送类似。如前所述,使用双口RAM的关键是解决左右端口同时操作同一RAM单元的竞争问题。图3中采用了硬件判优的方法,即将左右端口的BUSY信号经相应处理后分别引至支持插入等待时序的TMS320VC33和TMS320F240 的对应引脚,以解决左右端口对同一单元的争用问题。

为了使整个系统成为完全可编程系统,增加系统的灵活性,系统中逻辑控制选用可编程的逻辑器件GAL实现[5]。GAL选用Lattice公司的GAL20V8B芯片,并采用Lattice公司提供的ispDesignEXPERT集成开发软件对其进行逻辑编程。ispDesignEXPERT支持多种硬件编程语言,系统中采用ABEL语言进行编程。左、右两端GAL的输入管脚信号定义如图3中所示。

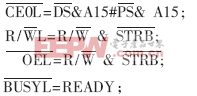

左端译码电路的逻辑方程为:

关键词: 系统 应用 导航 组合 RAM 双口 双口RAM TMS320VC33 TMS320F240 组合导航系统 CY7C028

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码