基于ARM和FPGA的声纳波形产生系统设

一般地,DDS输出信号频率![]() 为一个参考时钟周期内的相位增量,由此可得:

为一个参考时钟周期内的相位增量,由此可得:

由图2可知,![]() 相当与

相当与![]() rad,相位累加器溢出一次所历经的采样脉冲(参考时钟)个数与DDS输出一个周期的信号所包含的采样脉冲个数是相等的,即:

rad,相位累加器溢出一次所历经的采样脉冲(参考时钟)个数与DDS输出一个周期的信号所包含的采样脉冲个数是相等的,即:

将(1)式代入(2),可得:![]()

由(3)可知,在参考时钟一定的情况下,频率控制字 决定了DDS输出频率。 实际上改变的是信号的相位增长速率, 越大,相位累加的曲线越陡峭,溢出一次所需的时间越短,对应输出信号的周期也越小,输出信号的频率就越大;与此相反, 越小,相位累加的曲线越平坦,溢出一次所需的时间越长,对应输出信号的周期也越大,输出信号的频率就越小;当 按线性变化时,输出信号即为线性调频信号,改变 的变化规律,就可实现不同规律的调频,如双曲、指数、对数调频等。当 =1时,DDS输出最小频率:![]()

(4)式也是所谓的频率分辨率。

3、系统硬件实现

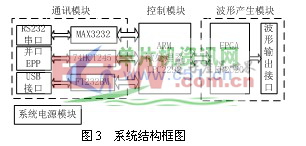

系统硬件设计采用模块化结构,由通讯模块、控制模块、波形产生模块和电源模块四部分构成,如图3所示。

3.1 控制模块及通讯模块

ARM作为控制模块的核心,选用Philips公司的ARM7TDMI系列微处理器LPC2292。控制模块和通讯模块实现了本系统与外部主控设备(一般为PC机)的通信,通过RS232串口,并口EPP或USB通讯接口,接收主控设备发出的声纳波形信号的幅度、频率、相位、带宽等参数控制字,用以控制波形产生模块产生相应的声纳波形。

3.2 波形产生模块

DDS技术的实现依赖于高速、高性能的数字器件,一般有两种方案,一种是使用DDS专用芯片,另一种用可编程逻辑器件FPGA自行设计。DDS专用芯片控制方式固定,价格较高,而FPGA以其速度高、规模大、可编程,以及有强大EDA软件支持等特性,十分适合实现DDS技术。本系统用FPGA实现DDS技术。FPGA选用Altera公司的Cyclone II系列的EP2C20F484C8N。

4、系统软件开发

本系统的软件主要分为主控设备应用程序设计,FPGA波形设计部分和ARM控制部分。

主控设备应用程序是在X86平台上,VC环境下开发的。主要功能是通过RS232串口,并口EPP或USB任何一种通讯接口,实现主控设备与ARM通信。ARM控制部分的程序实现对通讯接口的访问,并实现对FPGA的控制。

FGPA波形设计过程采用自顶向下模块化的结构,主要包括时钟模块、寄存器读写及控制模块、DDS模块,如图4所示。

相位累加器是决定DDS性能的一个关键部分,相位累加器设计的好坏将直接影响到整个系统的性能,因此要从FPGA内部结构出发,设计出既节约系统资源,又能大幅度提高系统速度和性能的累加器结构[3]。在设计相位累加器的加法器模块时不用库中提供的lmp_add_sub模块,而是采用流水线技术,使用Verilog HDL编程实现。流水线示意图见图5。

相幅转换采用ROM查找表法实现。主要考虑的问题是FPGA内部存储器容量的大小,而EP2C20内部有大量的ROM资源可利用,因此可直接调用lpm_rom模块来实现。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码