片上网络(NoC)技术发展现状及趋势浅析

再者,从通信带宽的角度,随着工艺的进步,计算访存比进一步增大,意味着基于该结构获得接近峰值性能的应用算法越少。这就引入了一系列问题,如何让众多处理器核有足够的数据可算?如何更充分地利用片上有限存储空间实现核间共享,以避免片外访存?如何充分利用有限访存带宽,尽量让访存通道优先满足处于关键路径处理器核的访问请求?最近美国Sandia国家实验室提出在多核处理器芯片上堆叠存储芯片,来解决带宽增长不足的问题,这或许是一种可行的方案。

总而言之,片上存储结构已经成为影响NoC性能的关键因素之一。

软件并行化问题

未来的基于多核的高性能处理芯片可能会遇到很多传统的串行程序自动并行化方法较难实施的应用。如果不能有效地利用NoC片上并行处理资源,则并行计算的实际性能将会很低,因此如何通过有效的方法和模型,充分地利用NoC的众多处理单元,并极大地降低应用的开发难度,便成为迫切需要解决的问题。

与并行计算机发展过程中遇到的问题相类似,NoC并行处理体系结构所面临的主要问题是如何将应用中蕴含的不同层次、不同粒度的并行性有效地提取出来并映射到多核的并行硬件结构上去。这一问题的解决涉及包括程序设计模型、程序设计语言、编译系统及硬件支撑等在内的多个方面。

总体来说,开发并行程序可以有三种途径,一是串行程序自动并行化。这条路目前尚未走通,更为实际的目标应为人机交互的自动并行化;二是设计全新的并行程序设计语言。这种方法的缺点是需要全部改写原有程序,对用户来说成本和风险也很高,且效率不能保证。但是,随着多核的出现,若面向大众推广并行计算环境,就必须有一种新的容易被接受的程序设计语言。目前国际上正在研究的新兴并行程序设计语言如IBM的X10、UPC(统一并行 C语言,C语言的扩展)和Titanmin(Java的扩展)等;第三条途径就是串行语言加并行库或伪注释制导语句的扩展,也即增加一个库或一些新的制导语句来帮助进行消息传递和并行。这正是MPI和OpenMP所采取的途径,也是目前比较容易被接受且性能较高的途径。但其程序开发效率很低,难度也比较大[7]。

功耗管理问题

虽然NoC有助于提高芯片的能效(Energy-Efficiency),但不能忽视,由于多核系统片上集成规模的大幅度增加,功耗问题依然突出。如何在NoC设计中提高能效,对众多计算资源进行调度管理以最大限度降低功耗依然是NoC设计所面临的重要问题之一。

从体系结构角度看,NoC主要包括处理器核、核间互连以及片上存储三个主要部分。NoC的低功耗研究可以围绕功耗评估,处理器核功耗优化,片上网络功耗优化以及片上存储功耗优化这四个方面对各部分展开,其中功耗评估是NoC低功耗设计的基础。

功耗是导致包括NoC在内的多核技术出现的重要诱因,也是片上多处理器设计的重要制约因素。对于NoC的不同设计模块和设计层次,都存在行之有效的降低功耗的方法,而这些方法又可能是互相牵制,互相影响的。因此需要贯穿NoC体系结构到电路工艺的各方面的丰富知识,才能在设计早期做出正确的多核架构的选择[8]。一般而言,从越高的设计抽象层次入手考虑低功耗设计问题,则可获得的降低功耗的效率就越大。

NoC发展趋势

技术发展趋势

·向层次化众核方向发展

微软公司2007年6月在美国西雅图召开了第一个以ManyCore(众核)为主题的研讨会(Workshop),标志着众核设计已经成为技术发展的趋势和学术研究的热点。

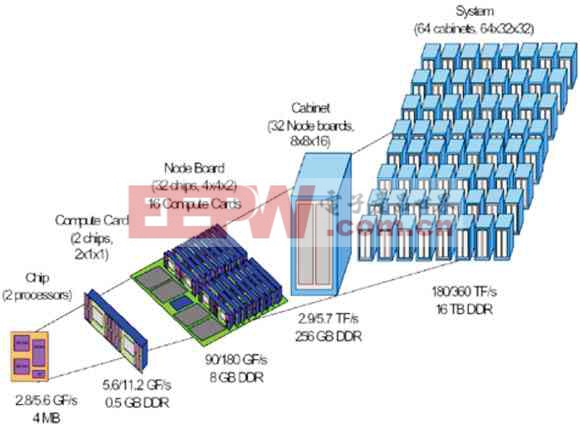

集成电路设计总是想方设法把现有的各种电子电路乃至计算系统集成到单一芯片上,因此计算机体系结构历来是集成电路片上系统架构的参考体系。超级计算机是最强大的计算机,充分参考超级计算机的体系结构是设计多核处理器的基本思路。超级计算机体系架构的基本特征就是小核大阵列和层次化管理。无论是世界排名第一的Roadrunner(122400个核),还是排名第二的BlueGene/L(212992个核),如图3所示,都是采用高性能、层次化、可扩展的巨大阵列,连接数目众多的普通微处理器(小核)来保障最优的性能。超级计算机告诉我们,小核大阵列和层次化管理必将成为众核处理器的主流技术发展方向。

图3 BlueGene/L的层次化阵列结构

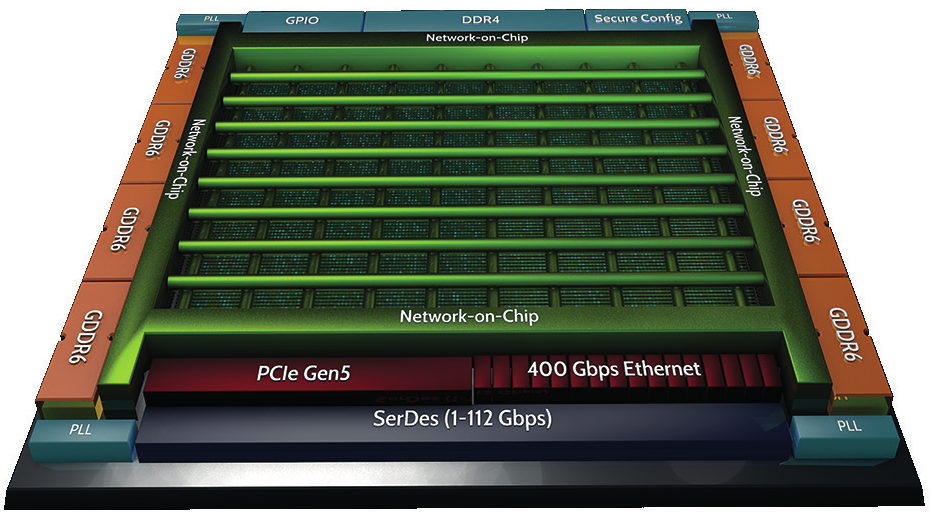

·向三维NoC方向发展

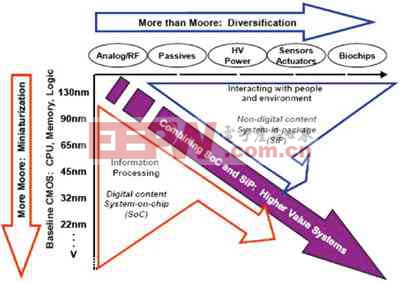

ITRS 2007年版阐述了More Moore(延伸摩尔定律)和More than Moore(超越摩尔定律)两个概念,如图4所示,其中延伸摩尔定律是按照等比例缩小继续走微细化的道路,而超越摩尔定律追求的是功能多样化,并指出下一代SoC(NoC)与SiP技术融合的发展趋势。

图4 ITRS 2007年版摩尔定律诠释图

正如ITRS所预测,在工艺技术发展和设计技术需求的双重驱动下,三维集成(又称为系统级封装,SiP)技术愈来愈受到学术界和工业界的关注和重视。NoC虽然克服了全局延迟过长带来的信号完整性及全局同步等一系列问题,但并没有在根本上解决缩短物理连线,减小信号时延的问题。由于二维 NoC布局条件的限制,难以保证关键部件相邻以缩短关键路径长度,而三维集成技术可把不同的器件层堆叠起来,不仅在真正意义上缩短了连线的长度,并克服这种布局的限制。因此把NoC和三维集成这两种设计技术融合起来的三维 NoC就显得自然且引人。

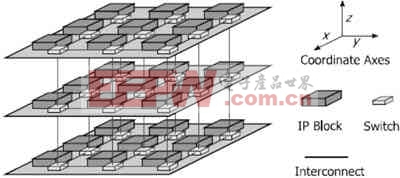

三维NoC是在单个芯片上将资源节点(Resource)分布在不同的物理层上,并用三维立体架构实现资源间的互连,以构建高带宽、低延时、低功耗的NoC系统。典型的三维Mesh结构NoC如图5所示。三维 NoC是一个崭新的研究话题,近两年才在国际上被提出(最早一篇相关研究论文于2005年公开发表[9])。目前从事该领域研究的学术机构包括美国斯坦福大学、加州理工大学、宾州州立大学、华盛顿州立大学,瑞典皇家工学院、日本的Keio University,加拿大的不列颠哥伦比亚大学,以及Intel、Toshiba等大公司的研究中心。可见,三维NoC已经引起了国际上学术界和产业界的注意,很可能在未来几年内发展成为一个重要的研究领域,并得到广泛的关注。

图5 三维NoC示意图

产业发展趋势

多核技术在产业界已有广泛应用。从Intel、AMD、SUN、CISCO等国际老牌企业,到PicoChip(2000年成立)、Ambric(2003年成立)、Tilera(2004年成立)等新兴公司,多核产品层出不穷;从超级计算机到PC机,从路由器等宽带应用到多媒体等嵌入式市场,多核产品逐渐广为人知。

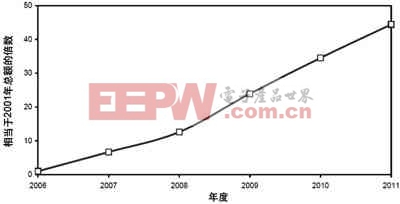

图6 多核技术市场容量图(来自VDC Research)

VDC Research于2007年发表了《多核计算的嵌入式应用:全球市场机会与需求分析》。报告分析了多核技术从2006年到2011年的市场需求走势,如图6所示。图中的纵轴是以2006年总值为单位1,其他年份与2006年相比多核产品市场总额的倍数关系。研究表明,多核技术到2011年,嵌入式应用领域的市场总额将超过2007年的6倍,超过2006的44倍。如此快速的增长速度决定了我国不应该介入太晚,否则就只能再次走“产品跟踪”的老路。

结语

包括NoC在内的多核技术是通用处理器技术升级的大方向已成为业内共识。多核技术是当代集成电路设计的战略性技术,它以很低的功率消耗、较强的并行处理以及优异的计算性能,征服了人们对集成电路性能的追求,“成为业界的重要里程碑”(Intel总裁语)。

先进的NoC结构可以通过集成现有的百兆频率核形成高性能多核处理器,大大降低了技术门槛,为中等设计公司带来了机会,目前已有一批中等公司和新兴公司在多核领域崭露头角,“国际寡头”垄断高性能处理器的格局正在发生变化。对我国现有设计能力而言,即使不能“一步登天”,但完全可以做到“所想即所得”,这亦为我国发展自主产权的高性能处理器产业提供了宝贵的契机。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码