时钟技术的未来发展:向分组网络转型(06-100)

就时钟技术而言,改进的 PLL 必须锁定于来自时钟卡的传统 TDM 频率,并同时生成 TDM 时钟频率和分组时钟频率(如25 MHz)。就性能而言,用于物理层同步的分组时钟频率比单纯的 TDM 频率对抖动性能的要求更高。抖动生成与衰减会对改造的PLL提出更高要求。

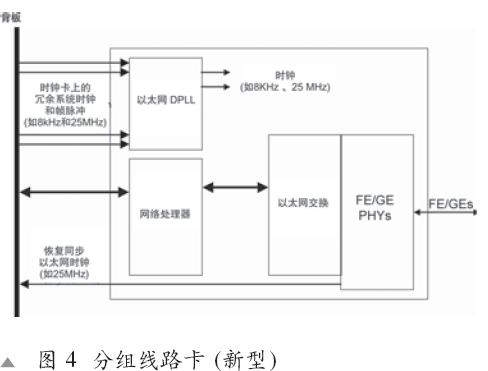

从背板到网络接口存在许多可能的时钟路径。首先,改进的 PLL 可为 FE/GE PHY生成 25 MHz 频率,以实现物理层同步。其次,改进的 PLL 还能为 CESoP 或 VoIP处理器生成 8 kHz 或 1.544 MHz/2.048 MHz 频率,进而为分组网络生成带嵌入时钟信息的分组。

从网络到背板也存在多种可能的时钟路径。首先,FE/GE PHY 可从物理线路提取频率为 25 MHz 或 125 MHz的时钟,进而分解为 8 kHz 频率并提供给背板上的时钟卡。其次,CESoP 或 VoIP 处理器能根据带嵌入时间戳的传送进来的分组进行自适应时钟恢复,从而为背板提供参考时钟。

分组线路卡(新型)

图4 给出了不带传统 TDM 背板且完全采用分组技术的设备。在此情况下,时钟很可能完全采用 25 MHz (或其倍数)的频率。这里给出的结构图显示了带 GE/FE接口的分组线路卡。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码