基于BiFIFO的多DSP高速互连系统设计

摘 要:在由TMS320C6701组成的多DSP并行信号处理系统中,DSP片间的互连性能成为系统性能的关键指标。本文从硬件和软件两个方面讨论了基于BiFIFO的DSP间高速互连的设计方案。

关键词:DSP互连;TMS320C6701;BiFIFO

引言

在一些应用中需要利用多DSP进行阵列运算。而在多DSP系统中,DSP间的数据交换能力已经成为系统性能的瓶颈。

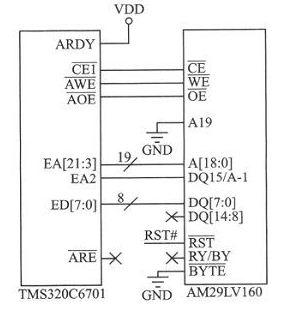

在由TMS320C6701组成的多DSP系统中,DSP互连方案主要有:通过BiFIFO(双向先进先出存储器)直接互连;通过DSP的HPI接口互连;通过DSP的McBSP接口互连。本文设计的高速并行信号处理板采用BiFIFO直接互连方案,该板上的两片TMS320C6701之间通过一片BiFIFO芯片(CY7C43684)交换数据。

BiFIFO芯片CY7C43684

CY7C43684是Cypress公司推出的高速低功耗CMOS同步BiFIFO,该芯片片内有2块独立的16K

关键词: BiFIFO DSP互连 TMS320C6701

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码